请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/783219/sn74hc595-the-problem-of-usage

器件型号:SN74HC595尊敬的所有人:

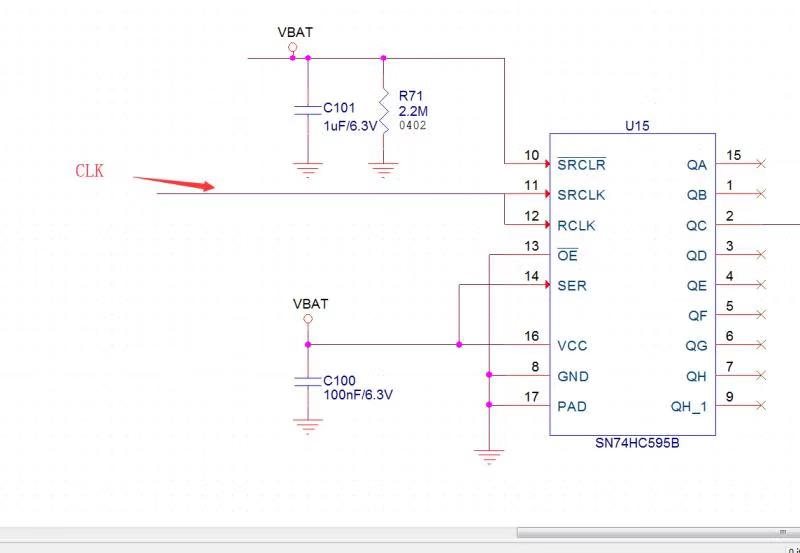

我使用 SRCLR=1、Oe=0、SER=1、SRCLK 被连接至 RCLK

我要实现该功能的目的是触发 CLK 高电平、第一个高电平的输出;然后触发 CLK 高电平、第二个输出高电平;等等

电路图如下:

但现在我手动接触 CLK 的 VBAT、然后释放。输出全部为高电平。 我连接了输出端的 LED 灯、LED 灯都很亮。

为什么是这样? 你能给我一些建议吗?

我使用的是国内595、在这个电路和这个方法测试中、结果是触发一个高电平、一个高电平的输出、等等