Other Parts Discussed in Thread: SN74AVC2T45, SN74AXC4T245, SN74AXC1T45

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/781527/sn74avc2t45-74avc2t45

器件型号:SN74AVC2T45主题中讨论的其他器件: SN74AXC4T245、 SN74AXC1T45

您好!

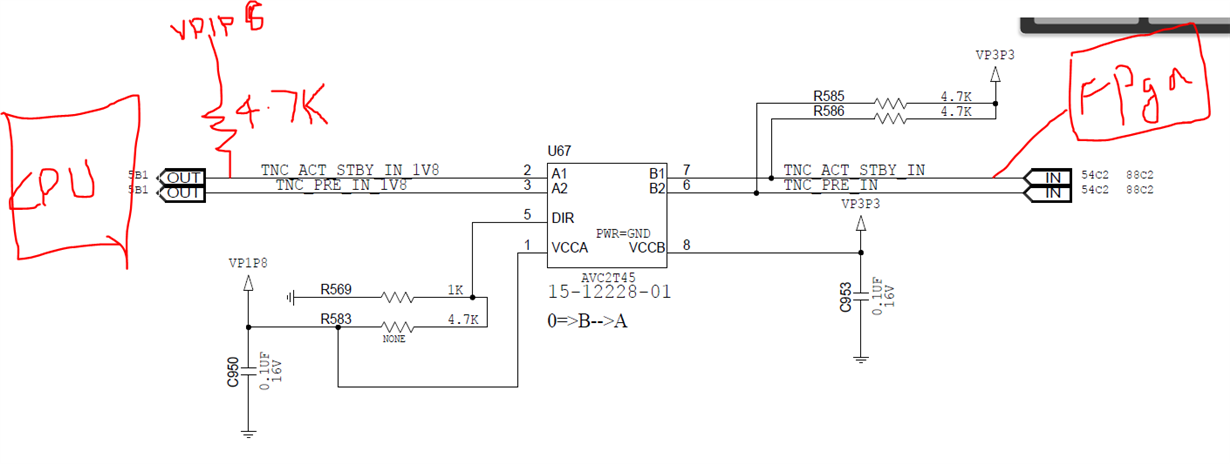

我对 SN74AVC2t45器件有疑问。 我从数据表中了解到、当没有 Vcca 或 vccb 或两个 I/O 处于高阻抗状态时。

我在电路的实现中看到了不同的行为。 所以、我想了解原因。 我正在附加架构以供参考。

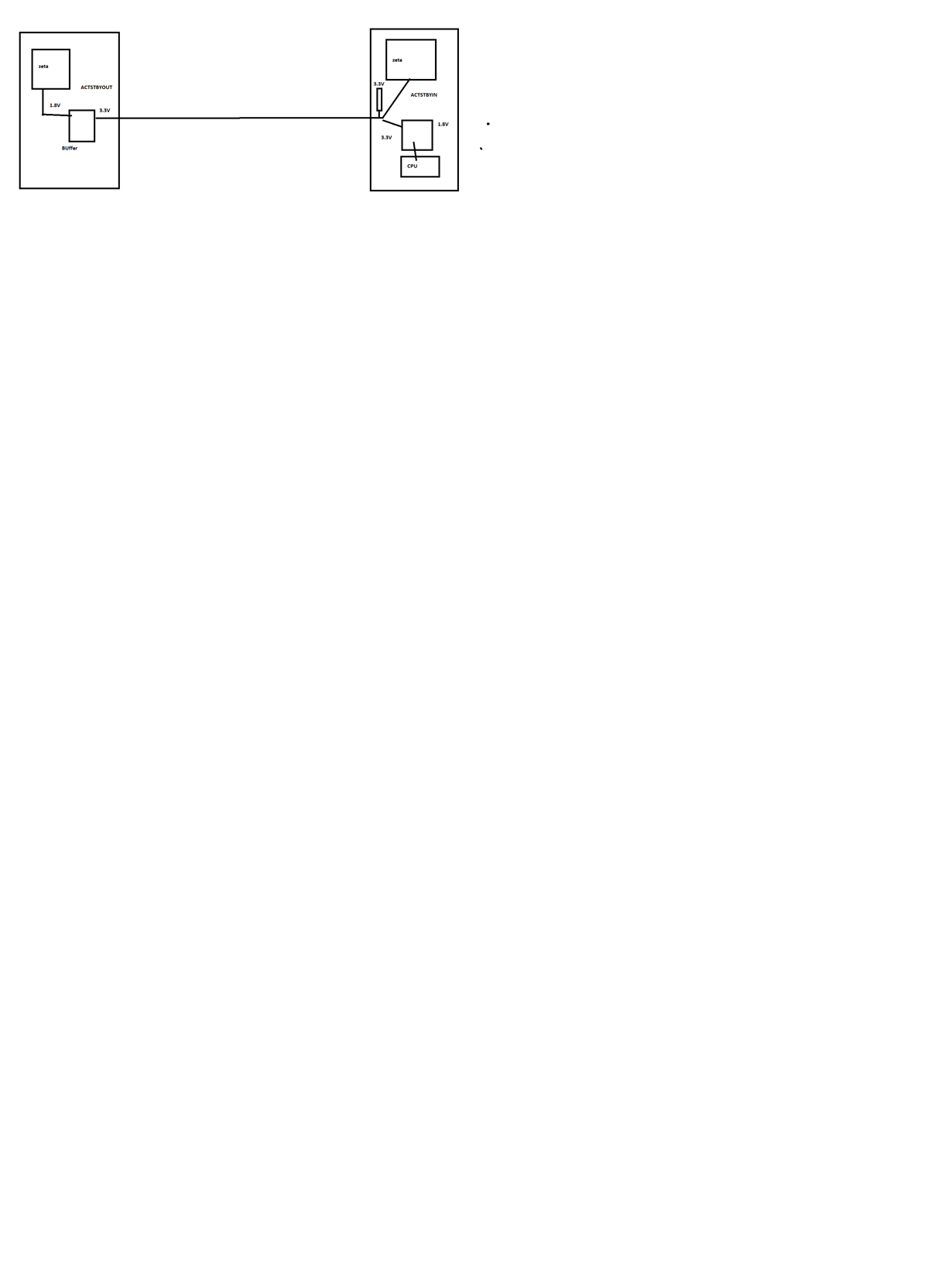

我们的系统中有2个通过控制线路通过缓冲器(AVC2t45)连接的卡。 信号从卡 A 传输到卡 B

1、当我们对卡 A 执行下电上电时、我们看到缓冲器输出立即变为3.3V 低电平。 因为卡 B 上有上拉电阻、它是否应该保持高电平?

2.当74AVC2t45由于 电源电压下降而具有高阻抗时、灌电流如何获得路径。

请告诉我是否需要澄清。 我可以提供更多的解释。