主题中讨论的其他器件: Mio

您好!

我将 TXS02612用作 SD 卡电压电平转换器、搭配 Zynq-7000 Xilinx FPGA 使用。 Xilinx 应答记录 AR# 63913 (Zynq - ZC702和 ZC706上的边际 SDIO 时序可能会在启动对 SD 器件的写入时导致数据 CRC 错误)建议在使用电压电平转换器时"可能违反 SDIO 规范中定义的2.0ns 输入保持时间"。 要解决此问题、"SD_DAT[0:3]和 SD_CMD 线路必须延长、以补偿电平转换器数据表中指定的最大通道偏斜"。 (www.xilinx.com/.../63913.html)

此建议也在 Xilinx Zynq-7000 SoC PCB 设计指南(UG933 -部分 MIO/EMIO IP 布局指南- SDIO (v1.13.1 p.68)中提供。

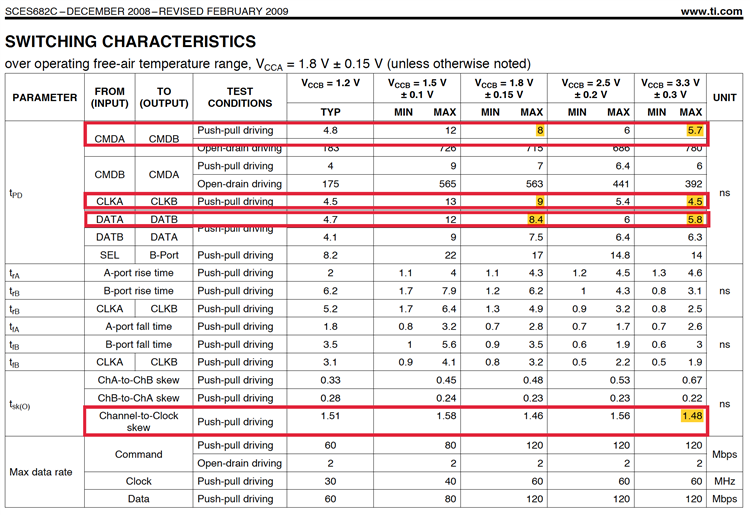

当我查看 TXS02612数据表中 VCCA=1.8V 时的开关特性(表见第12页)、CMD/DAT 从端口 A 到端口 B 的 tpd (最大值)不一定高于 CLK 的 tpd (最大值)。

-当 VCCB=1.8V 时、针对 CMD (8ns)和 DAT (8.4ns)的 tpd (max)小于 CLK (9ns)的 tpd (max)。

-相反、当 VCCB=3.3V 时、针对 CMD (5.7ns)和 DAT (5.8ns)的 tpd (max)高于 CLK (4.5ns)的 tpd (max)。

根据这些特性、可以得出结论:在某些情况下、缓冲器通道间时钟偏差可以为正(CMD/DAT 的缓冲延迟高于 CLK 的延迟)、在其他情况下、缓冲器通道间时钟偏差可能为负(CMD/DAT 的缓冲器延迟小于 CLK 的延迟)。

为了正确补偿 PCB 上的 TXS02612通道偏斜:

-我需要知道 VCCA=1.8V/2.5V、而 VCCB=3.3V、如果数据表中给出的通道到时钟偏移(tsk (o))始终为正、即 CMD/DAT 端口的缓冲器延迟保证高于 CLK 端口的缓冲器延迟?

谢谢你。