尊敬的 TI 社区:

我们正在使用 ADC 芯片测试设置、该设置使用 TXDB0108将连接到 Kintex7 FPGA 的1.8V 数据线路升高到2.5V。

该引脚排列如下:

VCCA 为1.8V、而 VCCB 在2.5V 电源轨上。电平转换器两侧的每条数据线路上都有串联电阻(值为10欧姆)。

受测的 ADC 芯片的采样率为2.5MSPS。 OE 通过10k Ω 电阻上拉至 VCCA。 我们在两个电源上都有0.1uF 旁路电容器。 我们当前面临的问题是、只要 ADC 开始转换并且线路上的数据可用、我们就会观察到耦合到电源的高频噪声。 当电平转换器的通道上没有数据时、我们不会看到该噪声。 为了确认该噪声是来自 ADC 还是来自电平转换器、我们断开了 ADC 的芯片板并向其中一个通道提供了方波。 信号的频率为2.5MHz、我们在数据线路和电源上观察到了相同的噪声模式。

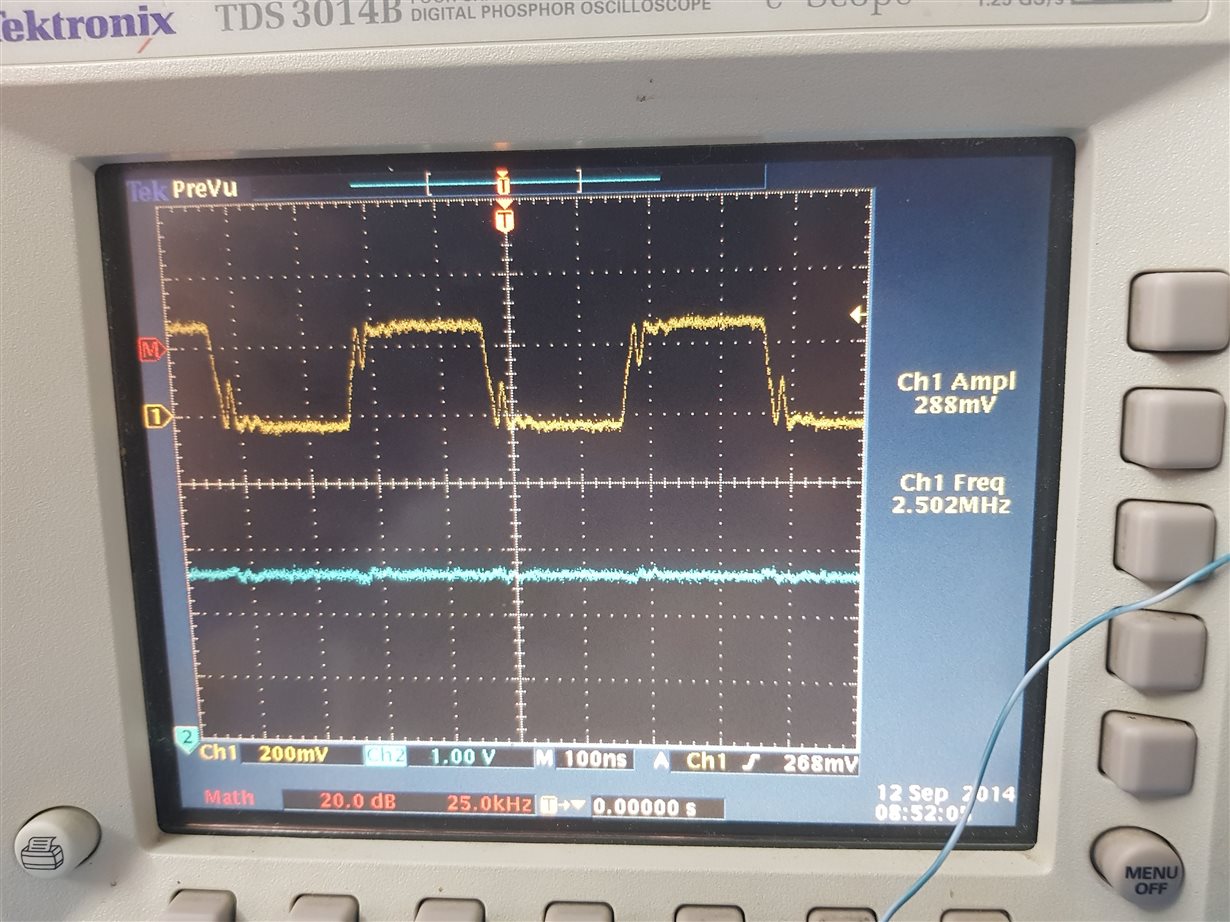

在此图像中、通道1是电平转换器通道 B 侧的2.5MHz 信号、通道2是电平转换器的 VCCA、电压为1.8V。 我们将观察信号中的振荡。

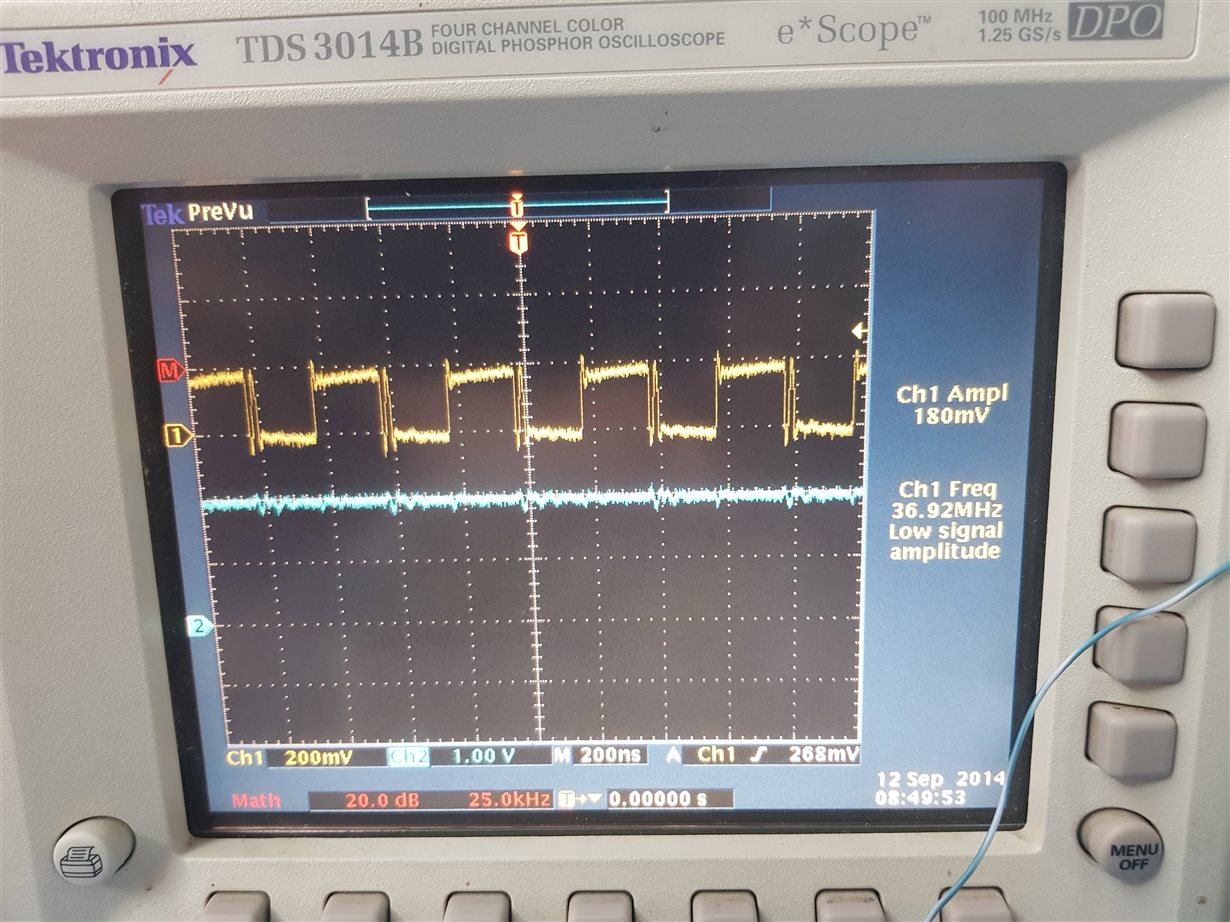

下图的通道1显示了电平转换器通道的 A 侧、该通道是从源提供的2.5MHz 信号、而通道2显示了电平转换器的 VCCB、即2.5V。 两个电源上都出现噪音。

下图的通道1显示了电平转换器通道的 A 侧、该通道是从源提供的2.5MHz 信号、而通道2显示了电平转换器的 VCCB、即2.5V。 两个电源上都出现噪音。

您可以看到、耦合到直流电源的信号上会出现明显的噪声。

现在、我们之前在电平 转换器附近安装了0.1uF 旁路电容器以确保正常运行、但在观察到这种噪声后、除了0.1uF 电容器外、我们还焊接了10nF 电容器。 令我们失望的是,没有任何改善。

我们需要您的帮助来消除此噪声、因为这会降低 ADC 芯片的 SNR。 如果您需要更多信息、请告知我们。 希望能提供紧急帮助。

马文·M.