我计划将多个移位寄存器链接在一起以获得更多状态。P/N #54HC595 (8位移位寄存器)的数据表具有 QH 输出和 QH 输出。 QH'输出大约是 QH 信号后半个时钟周期。 为了将54HC595移位寄存器中的两个连接在一起、我认为应该将 QH 信号发送到下一移位寄存器的"SER"引脚。 您能不能告诉我对合并两个54HC595移位寄存器的理解是否正确。 感谢 Bob Wagner。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我计划将多个移位寄存器链接在一起以获得更多状态。P/N #54HC595 (8位移位寄存器)的数据表具有 QH 输出和 QH 输出。 QH'输出大约是 QH 信号后半个时钟周期。 为了将54HC595移位寄存器中的两个连接在一起、我认为应该将 QH 信号发送到下一移位寄存器的"SER"引脚。 您能不能告诉我对合并两个54HC595移位寄存器的理解是否正确。 感谢 Bob Wagner。

尊敬的 Bob:

您将从第一个移位寄存器向第二个移位寄存器的 SER IN 发送 QH'。

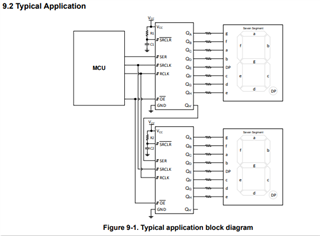

您可以参考 HCS595数据表 中的此图:https://www.ti.com/lit/gpn/sn74hcs595

您好、Albert、感谢您的回答。 我想我对54HC595的答案感到惊讶。 因此,您基本上说我应该将延迟信号 QH’发送到下一个移位寄存器,以获得16位的存储空间。

如果可以的话、我想比较一下获得16位存储器的类似需求、但是要比较另一个没有半帧延迟的芯片、即54HC166 (8位并行负载移位寄存器)。 该芯片没有延迟输出、而是 QH、类似于54HC595的 QH。 因此、在本例中、我认为要创建一个16位寄存器、我们会将 QH 发送到下一移位寄存器的 SER 中。 因此、如果这对于54HC166来说是正确的、那么为什么在原始情况下发送延迟。 现在您可以看到我的困惑。