请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1178553/sn74lvch16t245-sn74lvch16t245

器件型号:SN74LVCH16T245您好!

抱歉、我坚持这个话题、但我仍然无法完全理解。

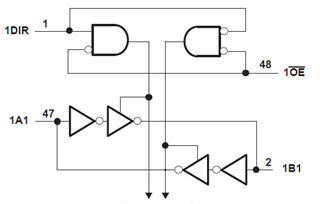

根据收发器的逻辑图:

并且知道 数据表中说"为了确保加电或断电期间的高阻抗状态、OE 应通过连接到 VCC

上拉电阻器"、

我仍然不明白为什么将 DIR 连接到 VCC 不能确保无论 OE 电平如何、上电或断电期间的输出具有高阻抗。

芯片内部的 OE 和 DIR 管理是否不同?

提前感谢您、

此致

皮埃尔