https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1178762/pga113-pspice-model

主题中讨论的其他器件:PGA113、 PGA113EVM-B、 OPA364您好:

TI 能否提供 PGA113 PSpice 模型 供参考?

Thx

此致、

Arang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1178762/pga113-pspice-model

主题中讨论的其他器件:PGA113、 PGA113EVM-B、 OPA364您好:

TI 能否提供 PGA113 PSpice 模型 供参考?

Thx

此致、

Arang

尊敬的 Arang:

PGA113是十多年前开发并推向市场的、 遗憾 的是没有为此器件开发 SPICE 模型。 熟悉该器件的最佳方法是通过我们的评估模块 PGA113EVM-B 我在 TI.com 上查看了库存、我们确实有此评估模块库存。

https://www.ti.com/tool/PGA113EVM-B

此致、

扎赫

尊敬的 Arang:

您似乎打算将 PGA113用作简单的可编程增益块来替代电路中的固定增益放大器。 PGA113具有一些附加功能、例如可用于系统级校准的输入多路复用器和内部校准通道。 您是否正在寻找包含校准或多路复用器功能的参考设计?

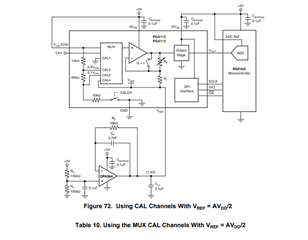

PGA113数据表中的图72显示了使用校准通道的典型配置。 请注意、Vcal/CH0必须连接到 ADC 基准电位才能使用校准(在该图中、它连接到 AVDD、因为这等于 ADC 基准电压)。 PGA113 VREF 引脚必须连接到一个低阻抗基准、此基准能够提供至少2mA 的拉电流和灌电流。 图72显示了采用缓冲器配置为 VREF 引脚提供低阻抗电压的 OPA364。

如果您不需要校准功能、则可以使用上面显示的配置、只需使用多路复用器选择 CH1作为输入即可。

我看到您的输入源在1550Hz 下预计介于30mV 和500mV 之间、但原理图未显示此参考值。 该30mV-500mV 输入信号是否以接地为基准? 还是以1.65V 中间电源为基准?

哪种类型的传感器连接到输入端? 如果此输入信号连接到外部世界、则在发生电气过载事件时、可能需要包含一些保护电路。 本文 提供有关电气过载保护的有用信息: https://www.ednasia.com/provide-robust-input-overvoltage-protection-for-amplifier-analogue-input-modules/。

此致、

扎赫