主题中讨论的其他器件:TINA-TI

对于 Tina ti、在4年后没有该芯片的仿真模型

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

对于 Tina ti、在4年后没有该芯片的仿真模型

您好 Rangel、

我知道这可能令人沮丧、但我们当时没有这样的原因与我们现在没有这种原因相同。

[常见问题解答]中对这些问题进行了说明为何单稳多谐振荡器件没有 PSpice 模型?

此致、

Owen

您好!

我正在尝试这种方法。

我已经向 DesignSoft 发送了一个问题。

如果您有一些建议、我会接受。

您好 Rangel、

一般而言、我建议您只对仿真脉冲进行硬编码。 为了确定实际器件的脉冲宽度和其他行为、我建议使用我们的 EVM 和样片器件构建原型。

-

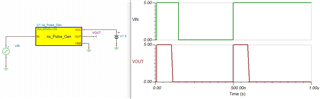

在 SPICE 中生成脉冲有很多方法--获得精确的单稳态多谐振荡器电路非常困难,但我可以很容易地帮助您使用脉冲发生器电路。

我的电路只观察输入是否处于高电平状态、然后在第二个信号中延迟这一状态、并将这两个信号与一些逻辑(一个反相输入和门)组合在一起、从而产生等于延迟的脉冲。

以下是 SPICE 代码:

* Pulse generator using RC delay element

.SUBCKT PULSE_GEN IN OUT VCC VEE

* Pulse width value is in nanoseconds

+ PARAMS:

+ PULSENS 100

* Input is buffered to avoid loading issues

* Threshold is set to VCC/2

EINBUF INBUF VEE VALUE = {IF(V(IN,VEE)>V(VCC,VEE)/2,1,0)}

* Threshold value for timer circuit (1 time constant)

VTHR VTH VEE 0.632119

* R*C provides delay for pulse generator

R1 INBUF TIMER {PULSENS}

C1 TIMER VEE 1E-9

* Delayed output from the timer

EDELAY DELAY VEE VALUE = {IF(V(TIMER,VEE)>V(VTH,VEE),1,0)}

* To get the delay, I multiply the input state (0 or 1) by the

* inverted delayed signal state (0 or 1) to get a short pulse

ELOGIC LOGIC VEE VALUE = {V(INBUF,VEE) * (1-V(DELAY,VEE))}

* I then use the VCC/VEE connections to determine the output voltage for the pulse:

EOUT OUT VEE VALUE = {V(VCC,VEE) * V(LOGIC,VEE)}

.ENDS

*$

和我的 TINA-TI 示例文件: