Thread 中讨论的其他器件: DM388、 WL1837、 WL1837MOD

大家好、团队、

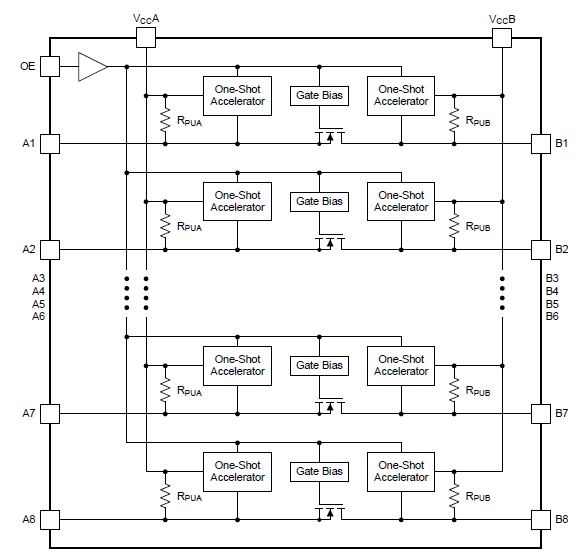

我的客户对 TXS0108E VIH 和 VIL 有一些疑问、可能需要您的信息。

在 TXS0108E 数据表中、当将 A 端口电源电压设置为1.8V 时、VIH 范围为1.6~1.8V、VIL 范围为0~0.15V。

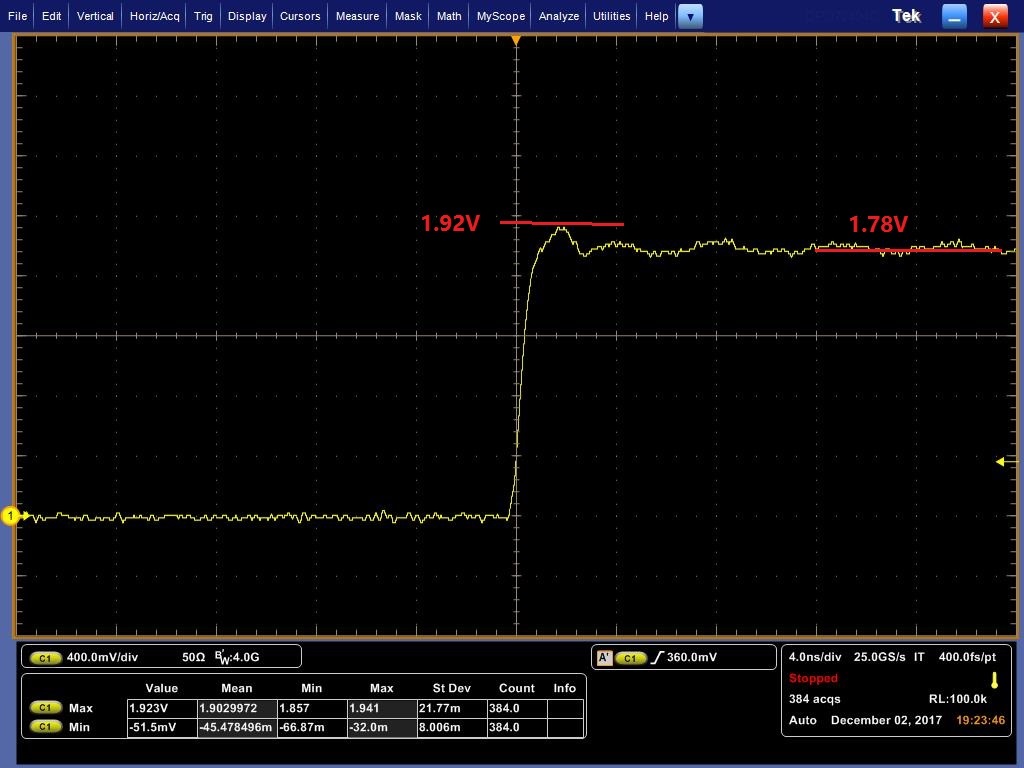

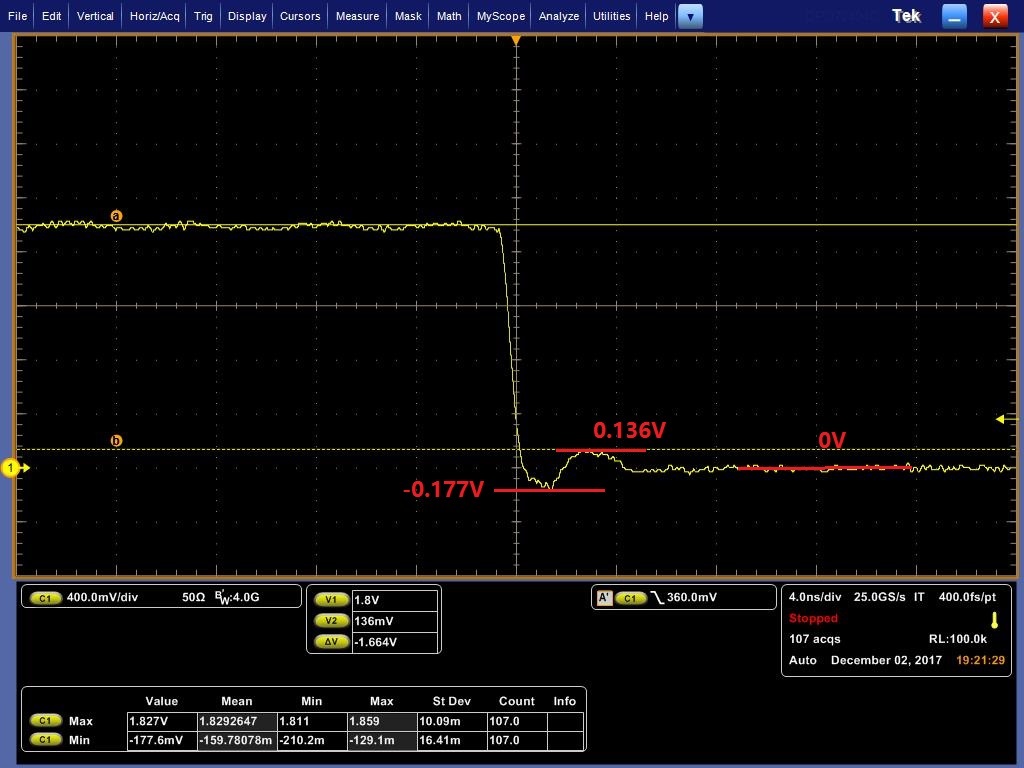

在客户测试中、A 端口信号电压如下所示。

对于低至高电平、过冲为1.92V、静态电压为1.78V。

对于高-低电平、负下冲为-0.177V、第一个振铃峰值为0.136V。

我的队列如下所示。

1. 对于高于 A 端口输入信号波形低电平、高电平和高电平的 TXS0108E、是否可以?

2. VIH/VIL 范围是否非常小? 例如,客户在 TXS0108E A 端口输入侧使用 NXP LS1043A,LS1043A 的规格为 VOH min=1.35V,VOL max=0.4V。 在这里使用 TXS0108E 与 LS1043A 有何风险?

谢谢。

Johnny