请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC16T245 大家好、

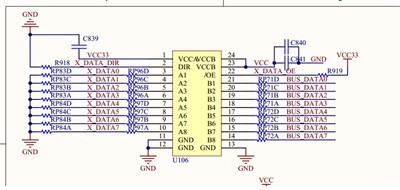

我的客户正在评估我们的 SN74LVC16T245。 加电期间发现一些异常输出干扰、原理图如下所示:

X_DATAx、X_DATA_Ox 和 X_DATA_DIR 由 CPU 的 GPIO 控制。 CPU 将在电源设置和稳定后200ms 输出这些 GPIO 信号。

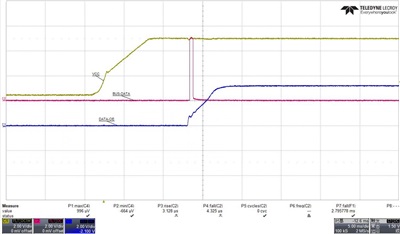

VCC 电源(B 侧)将在 VCC33 (A 侧)之前设置。 在此 阶段、输出 侧(A 侧) 将输出如下所示的异常脉冲 (Pls 请注意、在这种情况下、输入侧(B 侧)保持低电平):

客户想要了解这种干扰的根本原因、您能否在客户修复设计之前帮助解释这种异常脉冲衰减? 非常感谢。

此致、

张苏琳