主题中讨论的其他器件:SN74LVC1G17、 SN74LVC1G14

在几乎任何数字设计中、FF (触发器)的计时或复位几乎始终由某些逻辑条件决定。 例如:当 A = 47且 B 为 true 且 C 为 false 或 D 小于100且....时,必须重置计数器 等等 在任何应用中、复位 FF 的时间始终由栅极解码的某些组合条件决定。

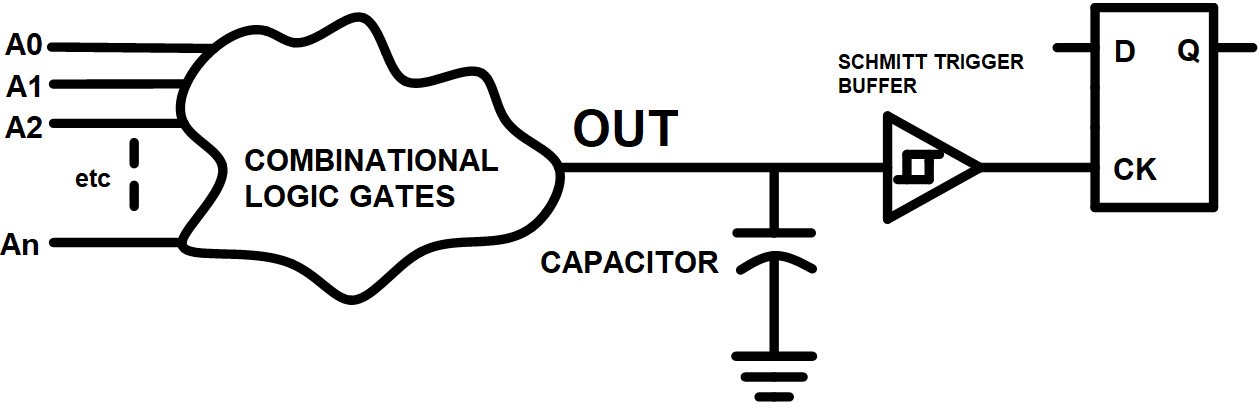

但是:任何一组解码某些条件(如上面的条件)的栅极的输出可能会受到干扰、可能会由于栅极延迟而产生虚假的不良响应。

我的问题是:

3 - TI 如何根据上面提到的某些条件复位74HC74触发器(或等效 D FF)、知道使用栅极对这种情况进行解码将会产生干扰/尖峰(在解码器的输出端)、这些干扰/尖峰可能(并且将)错误地复位 FF。

同样、在几乎任何数字设计中、对 FF (或像计数器这样的整个函数)进行计时是由一组门解码的某些逻辑条件决定的。 请记住、使用门解码可能(并且将)产生虚假响应和/或干扰、如何从解码电路为74HC74 FF 计时(并且将:Murphy 的法律真正有效!) 会有干扰?

如果这两个问题不够明确、请随时询问更多详细信息。

请告诉我们 TI 建议在上述上下文中重置(或时钟) 74HC74触发器(或等效)的方式。