请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC2G125 您好!

需要知道如何识别器件的引脚1。 我使用 的是 SN74LVC2G125DCUR - VSSOP (8引脚封装)。

我在一侧看到白线标记、而在数据表中、索引区域标记在一个象限上。 帮助我识别引脚1。 附加布局图以供参考。

我需要在白点附近有引脚1。 布局是否正确。

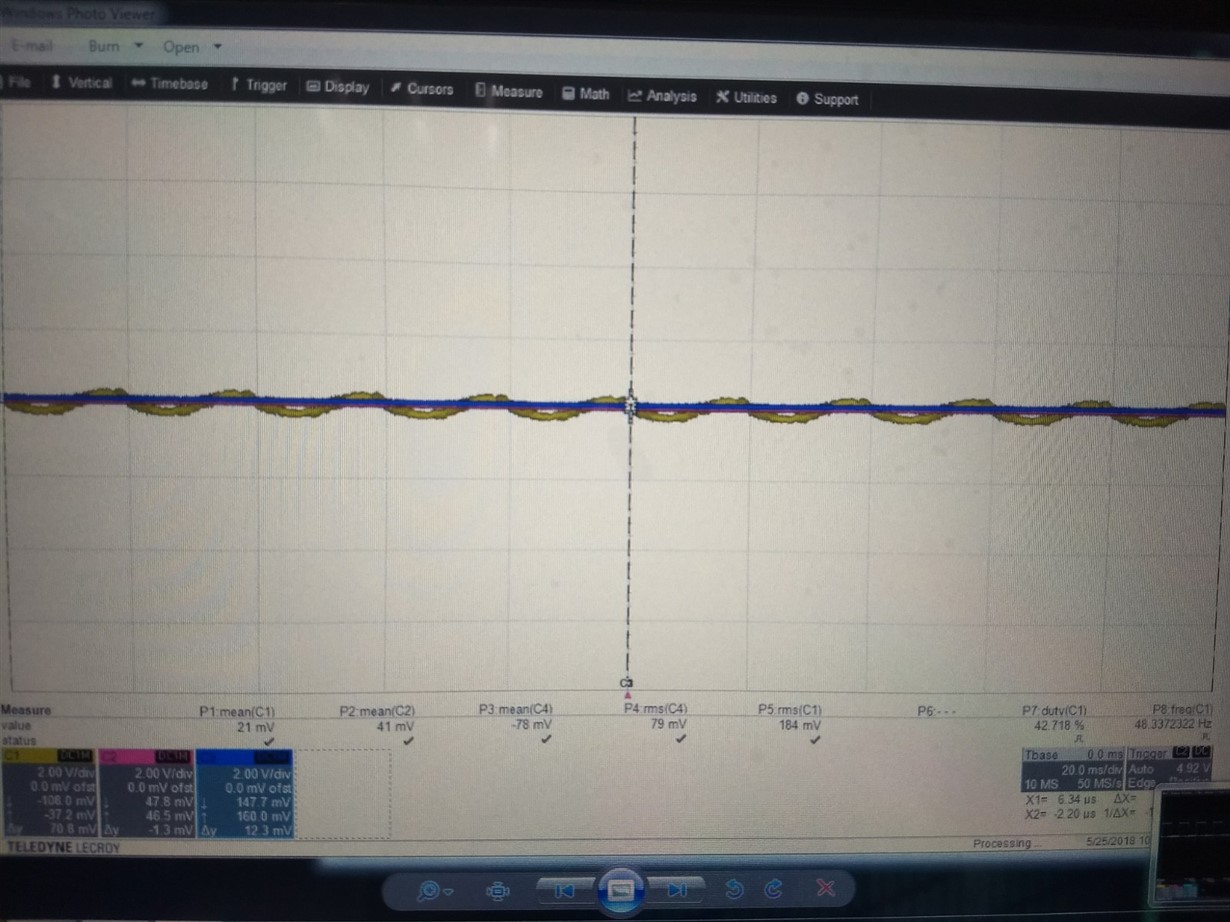

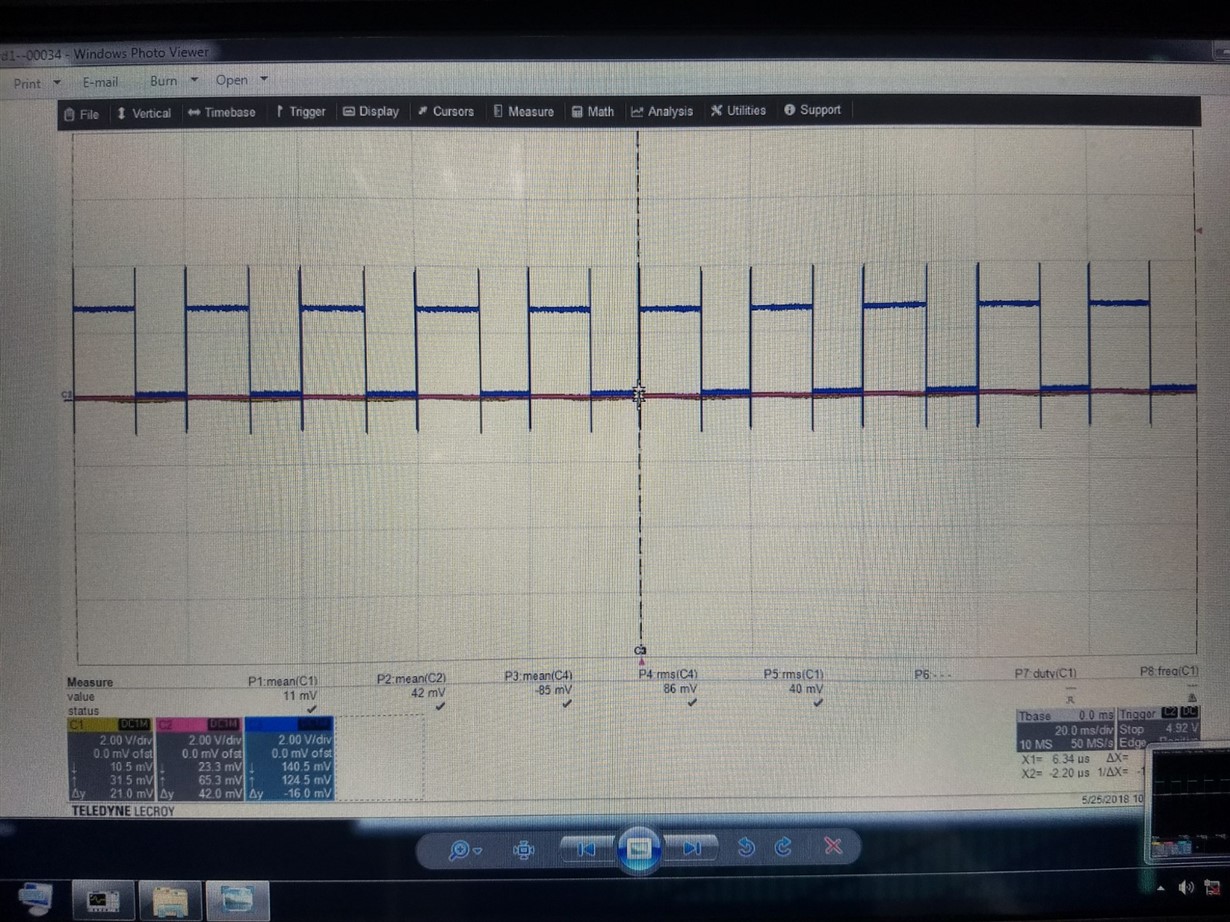

此外、根据数据表、当_OE 为低电平时、即0V、输出应与输入相同。 但在我的器件中、我看到它是反向的。 为什么会这样?

谢谢、此致

Arjun P Raj