主题中讨论的其他器件: SN74LVCR2245

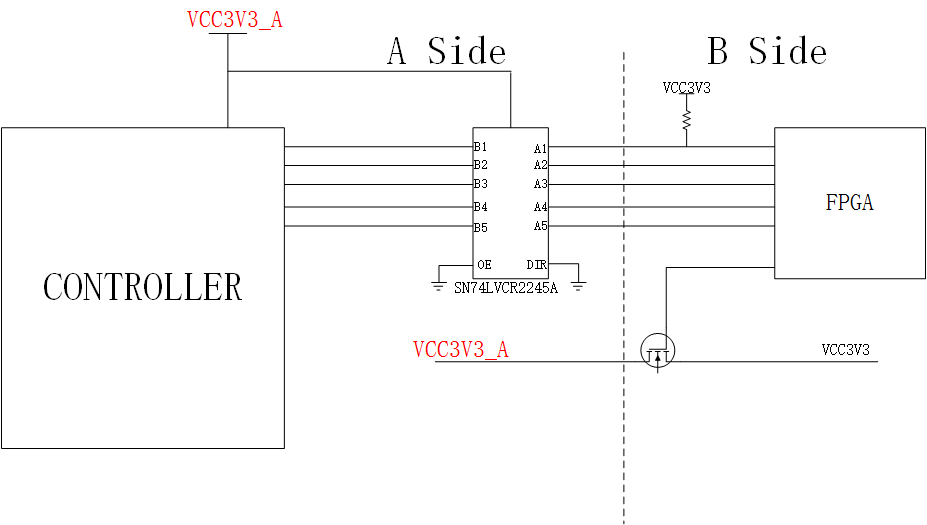

SN74LVCR2245A 用作电路中的缓冲器、信号定义形式 B 至 A、DIR 引脚和 OE 引脚连接至 GND

电源引脚连接到 VCC3V3_A 电源轨

系统加电、 SN74LVCR2245A 端口 A 侧信号加电优先、 电流回流功能正常、 部分断电 正常。 VCC3V3_A 为0V、 当系统打开 VCC3V3_A 电源轨、 SN74LVCR2245A 端口 A 侧和控制器上电时、端口 B 到端口 A 的信号正常

但是! 当系统关闭 VCC3V3_A 电源轨、SN74LVCR2245A 端口 B 侧且控制器 电源关闭时、 我 测试 VCC3V3_A 电压大约为 电源引脚中的1V 电压、

那么、部分断电为什么不起作用呢? 该电流是否从 A 侧回流到 B 侧?