尊敬的支持团队。

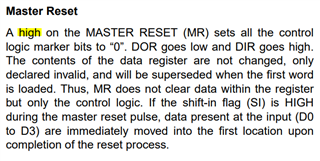

在"CD74HCT40105"的数据表中、主复位信号表示它通过输入脉冲信号进行复位。

请告诉我脉冲信号的详细信息。

・从上电到 MR 信号上升的低电平时间

・如果加电和 MR 信号上升时序相同、那么复位是否只能通过 MR 信号的下降来启用?

*在技术规格中,描述了复位脉冲的高电平部分的时间,但我找不到它的低电平。

此致、

Hiroaki Yuyama

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的支持团队。

在"CD74HCT40105"的数据表中、主复位信号表示它通过输入脉冲信号进行复位。

请告诉我脉冲信号的详细信息。

・从上电到 MR 信号上升的低电平时间

・如果加电和 MR 信号上升时序相同、那么复位是否只能通过 MR 信号的下降来启用?

*在技术规格中,描述了复位脉冲的高电平部分的时间,但我找不到它的低电平。

此致、

Hiroaki Yuyama

YUYAMA-SAN、您好!

[引用 userid="343895" URL"~/support/logic-group/logic/f/logic-forum/1185122/cd74hct40105-master-reset-mr-pulse-timing 在"CD74HCT40105"的数据表中、主复位信号表示通过输入脉冲信号进行复位。MR 输入受电平控制、但需要最小脉宽才能正常工作。

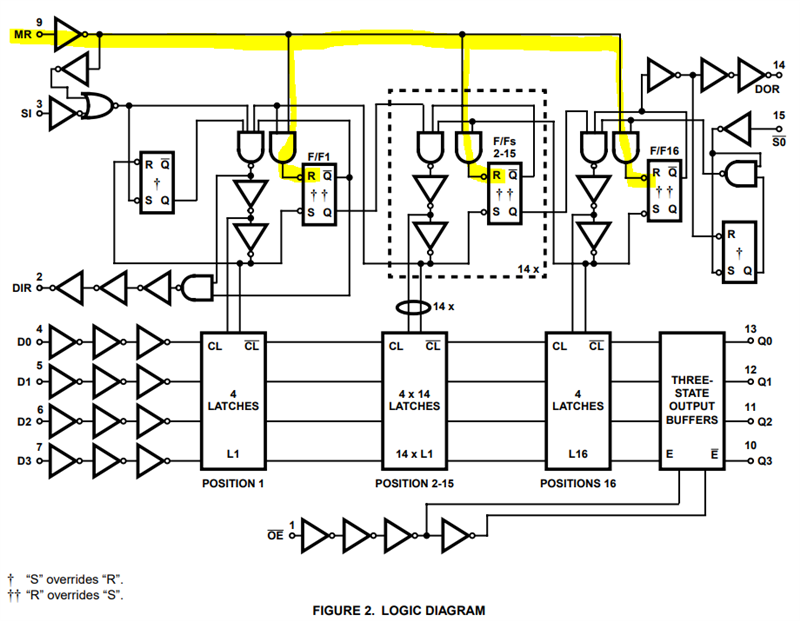

您可以在此处看到确切的逻辑功能:

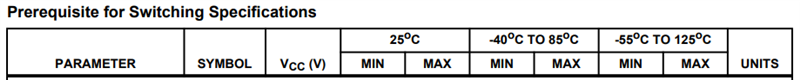

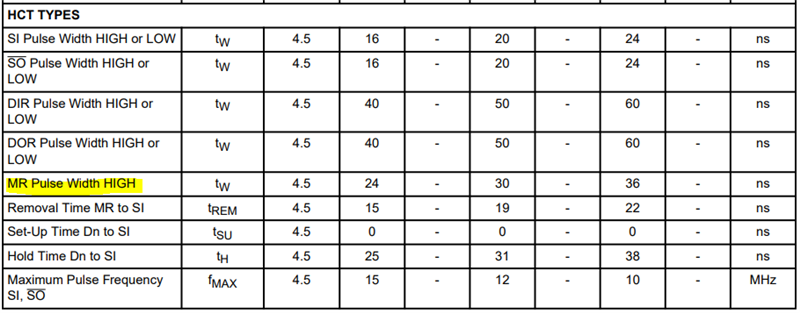

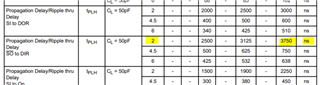

在数据表的"开关的必要条件"部分中、定义了 MR 输入的最小脉冲宽度:

这不是器件的规格。

我建议在开始运行之前至少提供数据表中提供的最大传播延迟时间、因为器件在启动时可能具有未知的内部状态、这是确保所有状态稳定的最短时间。

对于2V 操作、这将是3750 ns。

[引用 userid="343895" URL"~/support/logic-group/logic/f/logic-forum/1185122/cd74hct40105-master-reset-mr-pulse-timing・如果上电和 MR 信号上升时序相同、则仅通过 MR 信号的下降启用复位吗?否、MR 输入是电平触发的、它不是边沿触发的或脉宽触发的。 只要在电源处于建议的工作电压范围内且提供了最小脉冲宽度时 MR 引脚保持高电平、则器件的存储器将被清除。 请注意我在上面关于允许器件在开始运行之前保持稳定的回答。

Emrys-San、您好!

感谢您的回答。

我们知道 CD74HCT40105主复位输入是电平触发的、不是边沿触发或脉宽触发的。

在我们向客户提供的建议中、重要的是在接通电源后打开 MR 信号需要多长时间。

是否可以按照您的建议在开始运行之前至少提供数据表中提供的最大传播延迟时间?

例如、使用5V 电源时、建议的时间仅为700nsec。

问题的背景是将 FIFO 寄存器 IC SN74LS224N 替换为 Owen-San 建议的 CD74HCT40105E。

CD74HCT40105:将 SN74LS224替换为 CD74HCT40105 -逻辑论坛-逻辑- TI E2E 支持论坛

目前、主复位信号的上升时序和 CD74HCT40105的电源输入时序几乎相同、无法保证上述时间的安全。

我们猜测"由于复位不能正常工作、它无法正常工作"。

因此、我们将考虑满足上述规格的复位信号输入。

此致、

Hiroaki Yuyama