我们希望使用 TI SN74AVC16T245DGVR 将 DAC CLK 和数据[13:0]从1.8V (FPGA I/O)转换为3.3V (DAC I/O)。

DAC_CLK = 125MHz (tCLK = 8ns)。

原理图:

布局:

3V3 DAC CLK 和 DATA[13:0]布线全部位于 PCB 底部、并以50欧姆阻抗布线。

布线长度匹配、长度仅为~7.0mm。

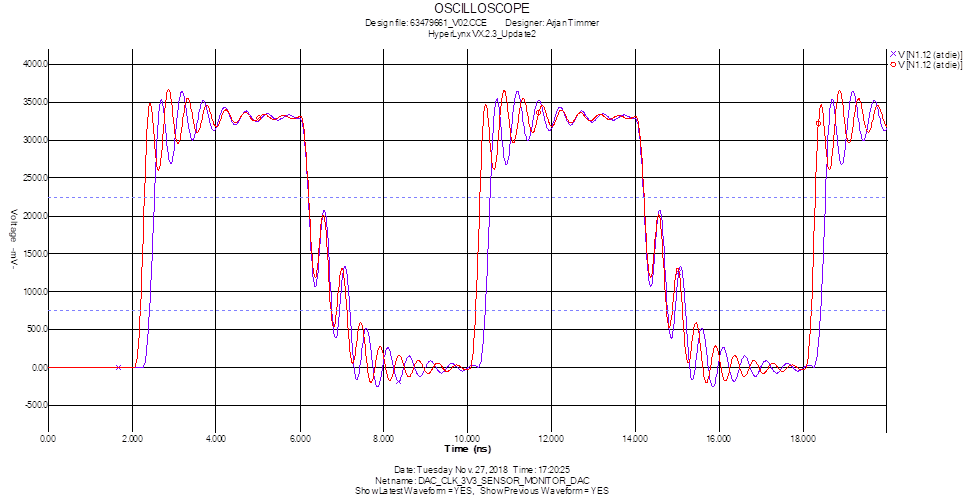

使用 HyperLynx 对所有信号进行了 Si 分析。

TI SN74AVC16T245DGVR IBIS 文件可从 http://www.ti.com/lit/mo/scem451/scem451.ibs 下载

Analog Devices AD9707 IBIS 文件从 https://www.analogue.com/media/en/simulation-models/ibis-models/ad9707.ibs 下载

1.8V 信号正常。

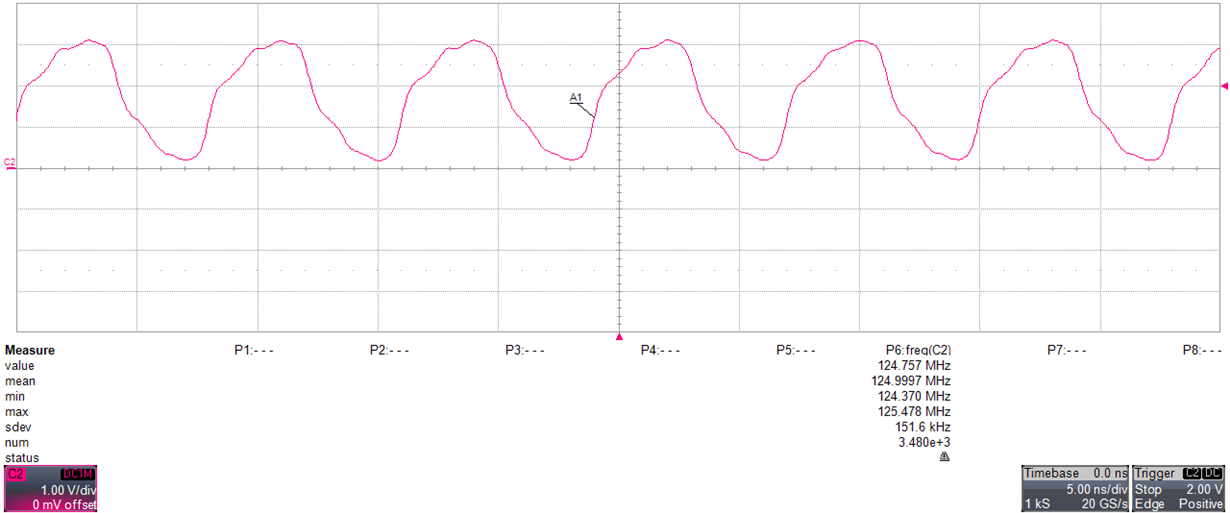

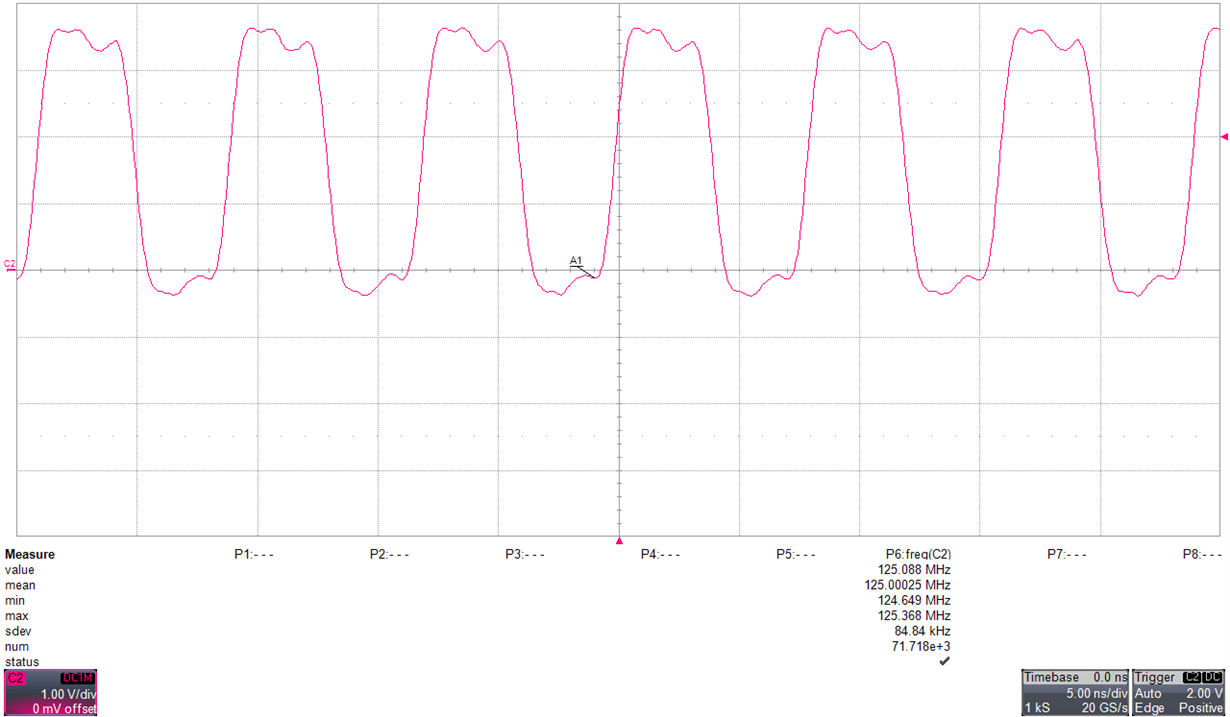

从电平转换器到 DAC 的3.3V 信号看起来都非常糟糕:

被称为可能解决方案的100欧姆串联电阻器不是一个选项、因为这个完全组装的 PCB 上没有足够的空间。

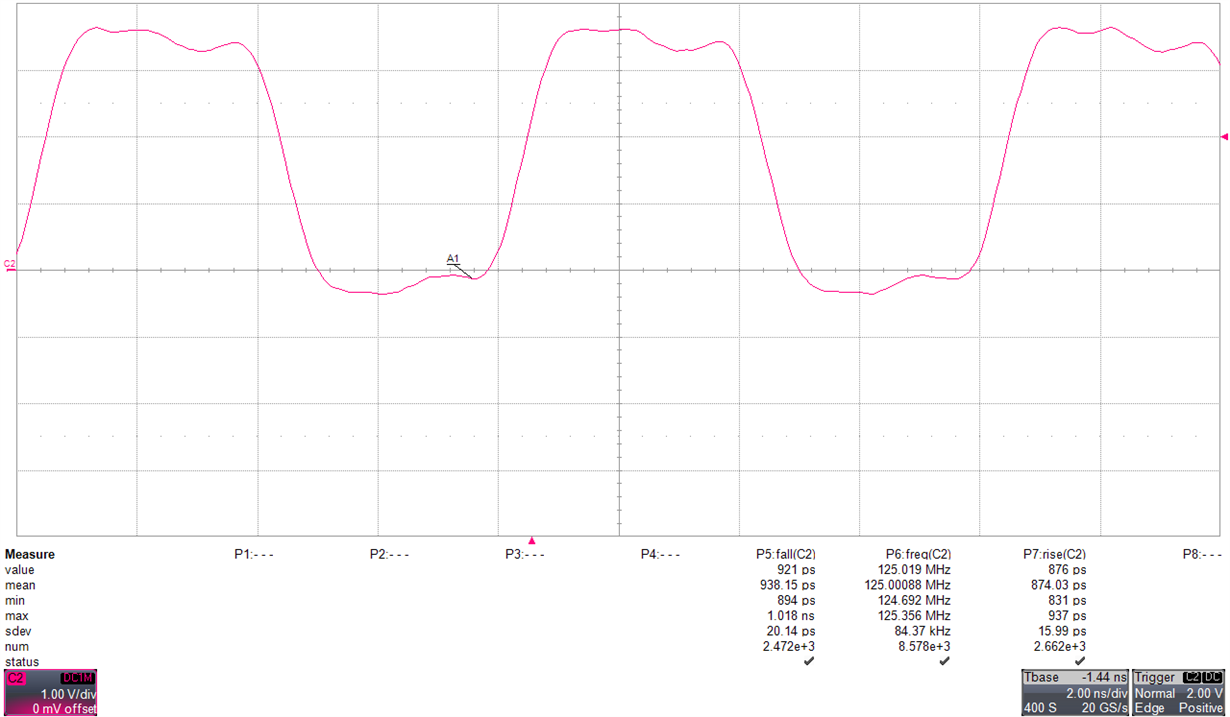

此外、信号的上升时间和下降时间非常不对称。 这使得 DAC 器件更难获得正确的设置和保持时间。

作为替代方案、在 SI 分析(74AVC16T245DGV)中使用了 NXP/Nexperia 的兼容电平转换器。

https://assets.nexperia.com/documents/ibis-model/avc16t245.ibs

这些结果看起来非常好、没有过度的振铃和对称的边沿。

从 TI IBIS 文件:T_fall =~3*t_rise

[斜坡]

| AVC16T245_IO_33

|可变 典型 值最小值

dV/dt r 1.97/2.35E-10 1.79/3.59E-10 2.16./1.73E-10

dV/dt f 1.95/7.46E-10 1.78/1.00E-09 2.1/3.31E-10

从 NXP IBIS 文件中:T_fall =~t_rise

[斜坡]

| AVC16T245_BION_33

|可变 典型 值最小值

dV/dt r 1.8726E+00/4.0904E-10 1.6970E+00/5.1595E-10 2.0455E+00/3.8291E-10

dV/dt f 1.8731E+00/4.1216E-10 1.6981E+00/4.1634E-10 2.0457E+00/4.2922E-10

您能解释一下 TI 器件出了什么问题吗?

此致、

Paul