Other Parts Discussed in Thread: SN74HCS125, TLV840, TLV809E

主题中讨论的其他器件:SN74HCS125、 TLV840、 TLV809E

在设备加电期间,我们注意到 IO 与总线保持状态是随机的,此时 IO 处于高阻抗状态。

我们想知道、通过上拉或下拉电阻将 IO 设置为与电平转换器相同的电压是否可以保证器件上电后 IO 处于已知状态。

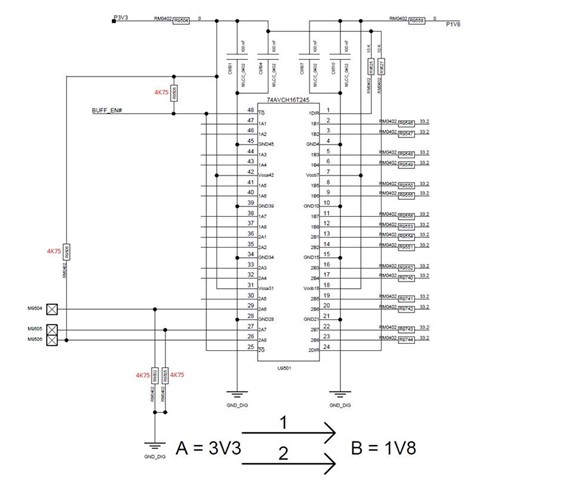

例如、如果我们有以下图表:

我们同时放置一个4k75 P3V3和 P1V8上升沿的上拉/下拉电阻。

我们是否可以确保总线保持将始终为以下状态?

*2A6:0V

*2A7: 0V

*2A8: 3V3

*2B6、2B7和2B8:随机(0V 或3V3)

-这是否由设计(具有所描述的总线保持状态的事实)来保证? 如果是、有哪些限制条件来满足这种情况?