Other Parts Discussed in Thread: TS12A12511, SN74LVC1G3157, CD4046B

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1189058/cd4046b-toggling-output-state

器件型号:CD4046B主题中讨论的其他器件:TS12A12511、 SN74LVC1G3157、

您好、E2E 专家、

你好。

40多年来、我一直使用该器件、主要用作 V 至 F 转换器。

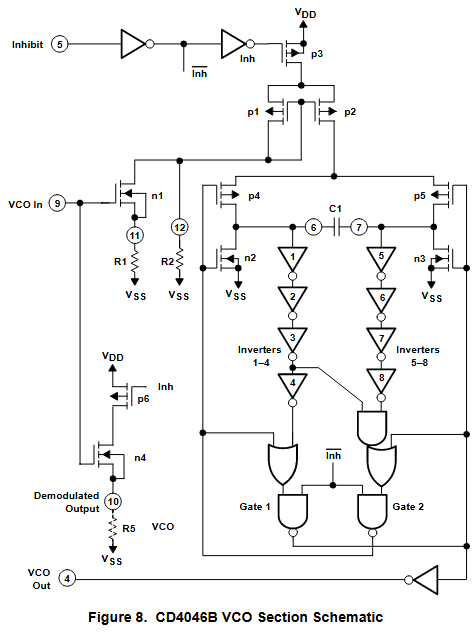

我在引脚9上施加电压、并监控引脚3上的方波频率。

是否有办法确保当输入电压为零时、输出也将为零(即、波形底部)?

目前、我通过电容器隔离我的外部电路、但如果可能、我希望消除这种情况。

其他信息:我尝试做的是避免消耗。 输入端无电压时电路中的任何电流。 我 µF 在输出端使用.22 μ F 电容器来实现这一点,但它会为我使用的扬声器提供失真波形。 是否有任何方法强制输出通过其中一个引脚进入零接地状态,因此我可以直接通过电阻器使用输出。

提前感谢您。

此致、

CSC