主题中讨论的其他器件: SN74AXC2T245、 SN74AVC2T244

您好、先生、

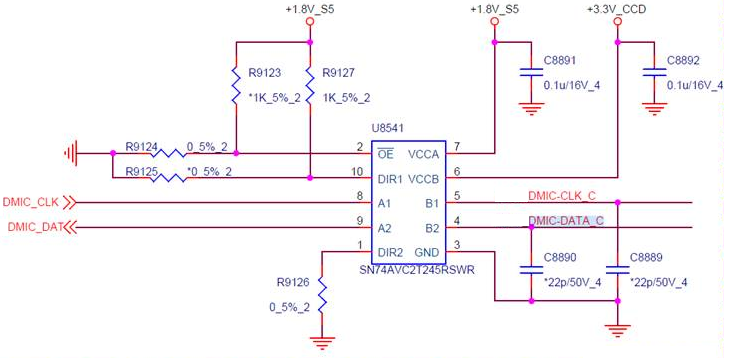

我们在客户工厂遇到了一个奇怪的问题、他们报告说他们设计了 SN74AVC2T245、用于将1.8V (PCH)电平转换为3.3V (DMIC 模块)。

但是、一些 DUT 不会显示从 DMIC 到 PCH 的正确数据、但实际上 CLK 可以传递到 DMIC。

以下是客户执行的一些测试、但未修复:

1.换用另一个品牌的 P2P 电平位移、然后正常工作。

2.重新连接 DMIC 模块有时会变得正常。

3.故障 DUT 将始终遇到问题。

4.移除 DMIC PDM DATA/CLK 上的 ESD、EMI 解决方案和任何电阻器。

以下是一些问题、需要您的支持来澄清更多信息:

1.客户发现一些 DUT 在启动时会发出一些噪音。 他们担心这会导致问题。 输入侧的 V LOW 是多少? 如果级别较低... 我们不应该打开迹线并输出任何东西、对吗?

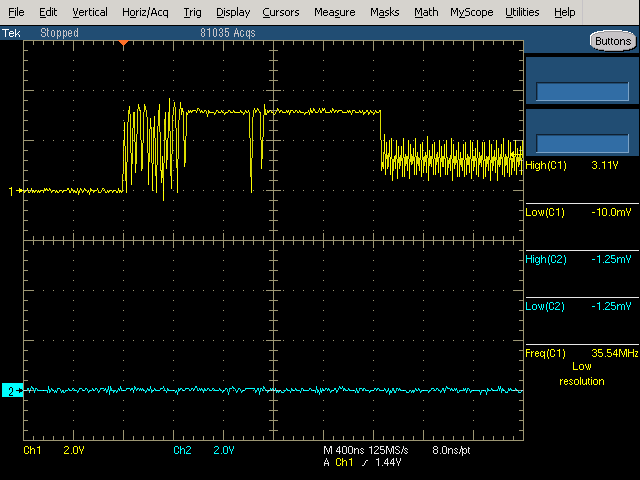

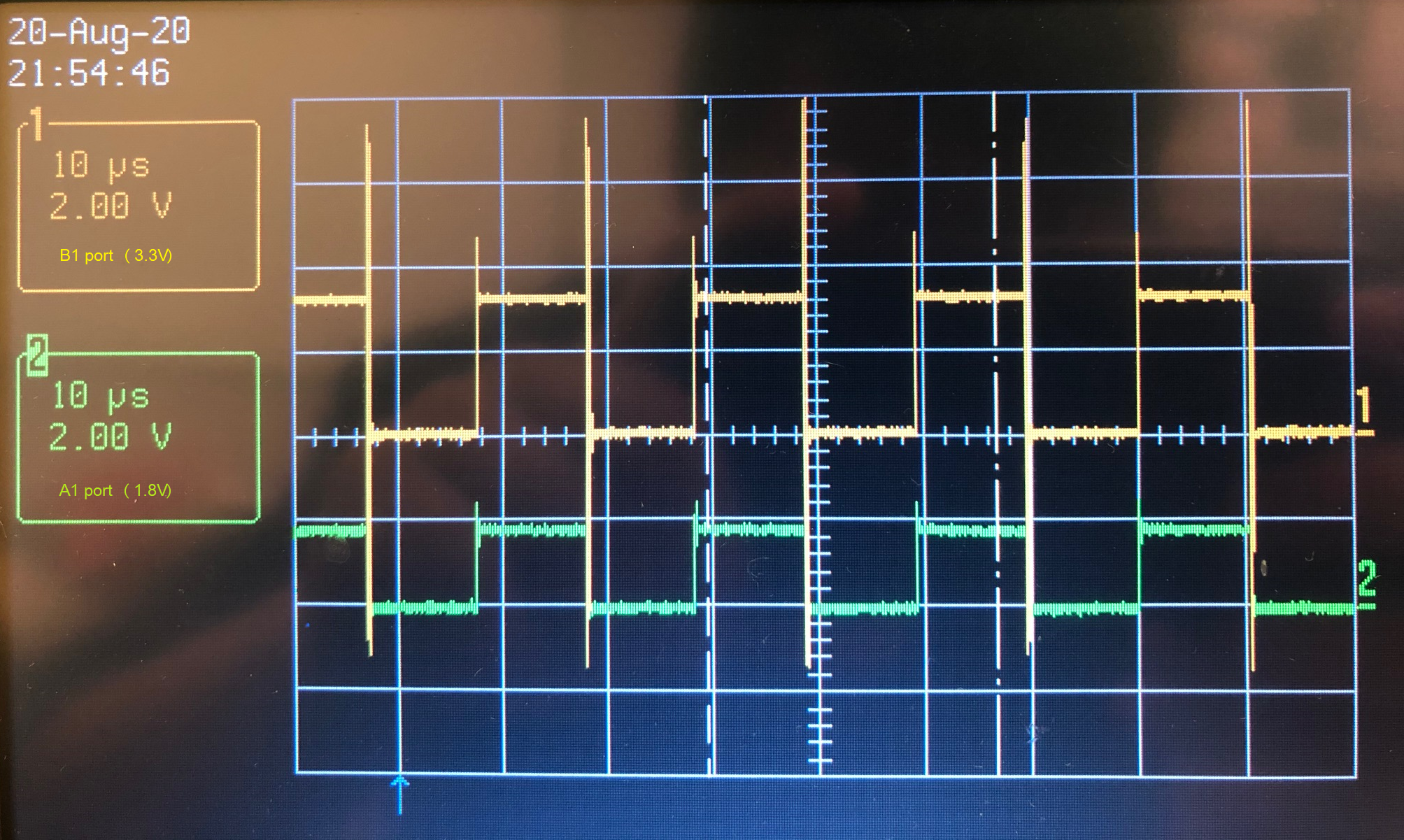

黄色为 B 侧(3.3V)、蓝色为 A 侧(1.8V)、同时... 1.8V 在0.4v 左右或更低(这张图片在正确的时刻无法捕捉)... 对于这种情况、应该输出噪声?

2. DMIC PDM CLK 的工作频率为2.4MHz…… SN74AVC2T245在处理该时钟速率时不会出现问题、对吧?

3.可以正确传送 CLK,但来自 DMIC 的数据不存在... 有什么想法或经验导致此情况?

期待很快收到您的回复、我们将感谢您的任何评论。

谢谢、

乔治