您好!

目前、我们遇到了74HC573芯片的问题、在下电上电期间、输出线路变为高电平~4.2伏。 硬件没有变化、电路在现场工作超过6年。 这是最近 PCBA 批次中提出的问题。

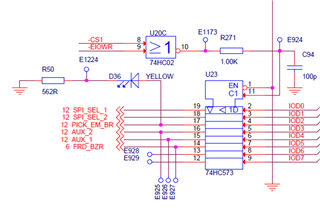

下面是电路 SNAP 和有关电路的详细信息。

这是应用电路、输入信号来自 CPU、默认情况下被拉高至5V。 这里的问题是、在工作板中、前信号 FRD_BZR 的输出信号将保持低电平、直到有来自 CPU 的一些数据。 但在不工作的电路板中、该信号在电源循环期间的短时间内变为高电平~4.2秒、在4.2秒后、电路根据应用正常工作。 这是报告的质量问题。

您能不能帮助解决这个问题。 我已经探测了工作电路板和不工作电路板的输入引脚7/OUTPUT 引脚14和锁存使能信号。 除了输出信号引脚外、两个电路板的输入和锁存使能都是相同的。14在不工作的电路板中会在短时间内变为高电平。

未连接问题板的波形。

问题板的波形、是输出信号(绿色)在短时间内变为高电平。

工作板的波形、在这种情况下、在下电上电期间输出(绿色)为低电平。