https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1222469/txs0104e-questions-of-txs0104e

器件型号:TXS0104E尊敬的团队:

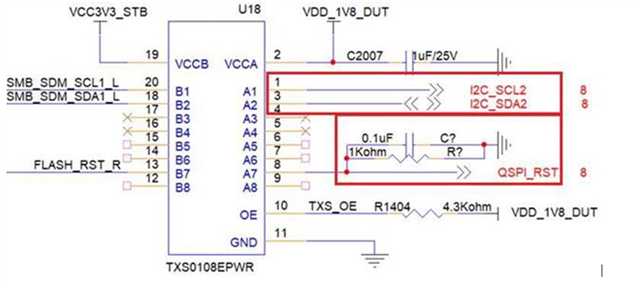

1.芯片的输出有容性负载限制:一次触发不要超过30ns 的要求。 但是、如下图所示的电路所示、QSPI_RST 在接地端添加了一个0.1uF 的电容器、信号的实际高电平和低电平变化时间约为0.6ms。 请确认其影响、是否有可能不考虑30ns 要求?

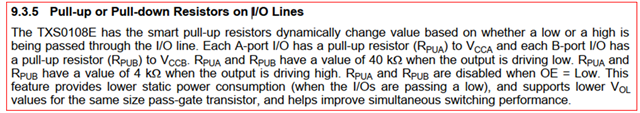

2.如9.3.5中所示,当输出为高电平时,有一个4K 上拉电阻器。 如果以下电路信号添加了1k 下拉电阻、实际输出高电平是否为1/5 VCCA (半高电平)、并且是否会导致信号异常工作?

非常感谢。

吉米