请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74AVC4T774 大家好、

我叫 Ives Li、是 SZ AA1团队的 FAE。

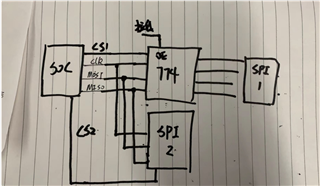

我的客户 TCL 在 其应用中使用了 SN74AVC4T774、如下所示:

他们发现、SoC 和 SPI2无法下拉来自 SPI1的 MISO 输入、这会影响 SPI2的工作方式不 正确。

他们尝试使用 SPI1的 CS 来控制774的 OE 来解决这个问题、您能帮助验证此解决方案是否有效吗?

更多信息:

- VCCA 和 VCCB 是3.3V ,当他们尝试输出一个低电平为 SOC 的 MISO 时,它只能下拉至2.5V ,而不能是0V。

-即使他们没有连接 SPI1器件, SoC 仍然无法拉低 MISO。

谢谢!

伊夫·李