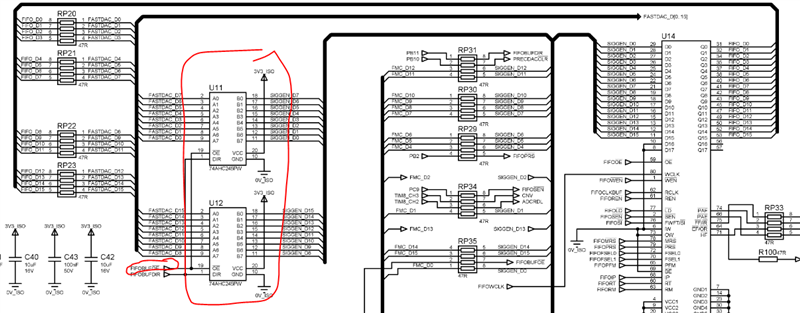

我在一个应用中、将74V293连接在微控制器和并行 DAC 之间、在两者之间提供"弹性"缓冲器、并使数据以良好受控的速率传输到 DAC。

我曾尝试过74V293的几种型号、包括 EP 版本以及-6和-7标准产品速度等级。

大多数时候、它运行良好、但在本应用中、大约每200倍从 FIFO 发出的数据就会与进入的数据不同。

没有明显的原因。 例如、我会监控 FULL 和 EMPTY 标志、但这些标志从不被置为有效。 当输出符合预期和不符合预期时、所有运行方面看起来都相同。

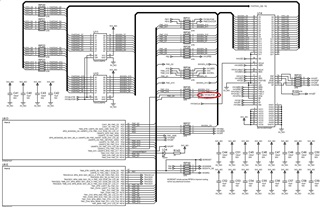

原理图如以下主题中所示: https://e2e.ti.com/support/logic-group/logic/f/logic-forum/874433/sn74v293-unexpected-offset-value

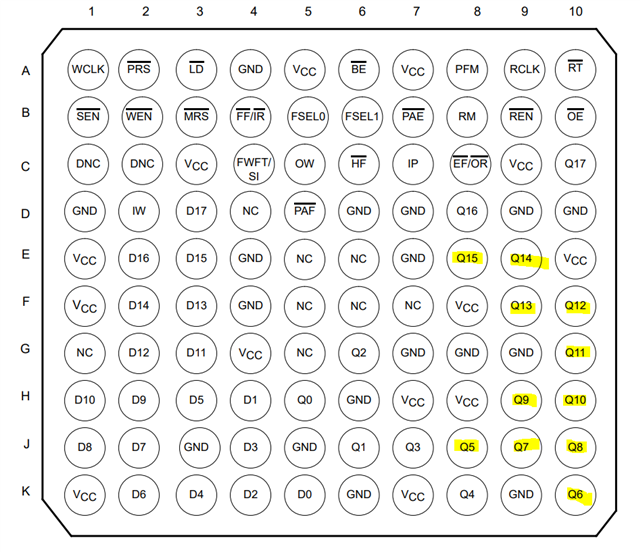

由于输出驱动一个16位 DAC、所以只使用 D0-D15和 Q0-Q15。 FIFO 配置为用作65536x18存储器。

数据以突发8192个值的方式写入 FIFO。 读数处于恒定25MHz。 微控制器会缓存写入的数据、因此以大约30M 值/秒的平均速率写入、但实际上以更短的脉冲形式写入、这些脉冲具有几个周期的长度、并且周期时间更短。

不过、我已经尝试延长数据设置时间、以便写入周期具有非常保守的时序。 但这并不能消除这个问题。

可编程空标志自动运行、被设定为49152、并被用于触发 FIFO 补充。

我只能使用16数字+ 2模拟通道 MSO 进行调试、因此无法轻松监控输入和输出。 如果我操作这个特定的 MSO 以便它记录时钟并行总线、那么我只能使用数据总线的14位来监控使能和时钟线路。

但是、通过单独监视输入和输出、我可以看到写入 FIFO 的数据始终正确、但输出中出现的内容有时会损坏。

通常、数据代表正弦信号。 为了尝试更多地处理正在发生的事情,我调整了代码,以便在发生这个问题时,写入的数据是一个从0到65535的线性序列,增量为2 (出于方便的原因,我不会在这里打扰)。

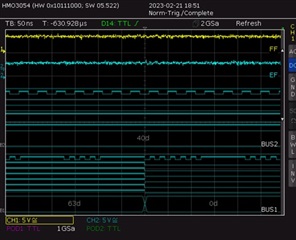

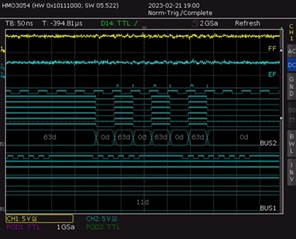

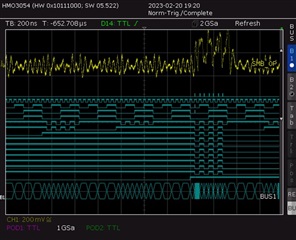

当这个线性测试序列被监控时、它立即变得清楚输出上正在发生什么:

(不知道为什么图像质量在上传时已经恶化了很多、但我认为它已经足够清晰了、可以跟随)。

顶部黄色迹线表示 DAC 输出:请忽略该图。 蓝色迹线来自顶部、REN、RCLK、Q2-Q15。

很清楚、每当输出位从低电平转换为高电平时、所有低位位、直至包括 Q5、然后在接下来的8个 RCLK 周期切换。

为便于理解、屏幕截图仅显示了位转换的选择。 但这种现象发生在 Q5-Q15从低到高的转换时、包括 Q16不存在的转换。

我不认为 REN 上的干扰是"真实的"。 我认为它们是一个不太理想的探测工件,这涉及到很多细小的电线,使板成为一个电孔。

什么导致了意外的数据模式?

几天以来、我一直在电路周围进行探测并尝试不同的测试、但没有找到任何可能导致这种情况发生的机制。

欢迎提出任何建议。

Colin