Other Parts Discussed in Thread: SN74LV4046A

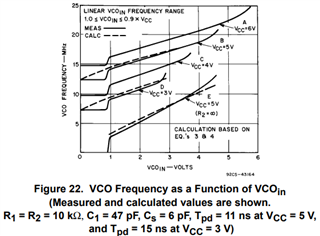

您好、我正在考虑使用 SN74LV4046A 将基础频率乘以10s kHz 的数量级、以获得2.4MHz 和9MHz 之间的可变频率。 参考时钟由微控制器生成、VCO 输出时钟馈入 FPGA、FPGA 将其进行128分频、然后发送到 SN74LV4046A 的比较输入。 我阅读了"CMOS 锁相环应用使用 CD54/74HC/HCT4046A 和 CD54/74HC/HCT7046A"、并且能够使用工作电路板来原型设计电路、这种电路板可以工作、但不稳定。 在我的电路中、C1为120pF、R1 3k、R2开路。 首先、我注意到、当 VCO 控制电压降至1V 以下(大约为2.5MHz 的 VCO 输出频率)时、VCO 输出频率会降至大约数百 Hz。 这是否与数据表中定义的1.1V 电压限值相对应? 对于某些输入频率、我可以看到输出频率振荡、就好像 PLL 未锁定一样。 我尝试了 C1和 R1的不同组合、但未能改进我的电路。 我还注意到、仅比较输出1和2的工作方式。 我的频率范围规格是否超出此组件的功能? 非常感谢