大家好、

我的客户对以下应用手册有疑问。

SLLA364A https://www.ti.com/lit/wp/slla364a/slla364a.pdf

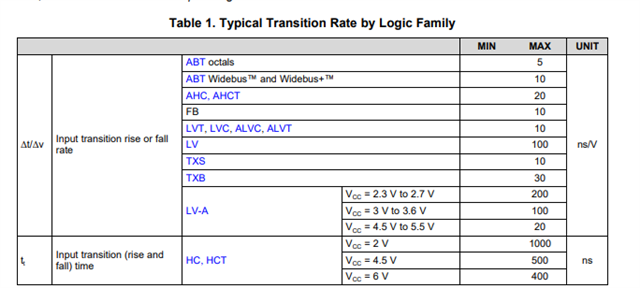

Δt LV-A 系列、则指定的转换率为 ΔV μ V/Δ t = 20ns/V (Vcc=4.5V 至5.5V)

我的客户想知道用于指定此规格的电压范围。

他们猜测 在考虑 输入 CMOS 的击穿电流的情况下、该电压将来自 VIL (max)和 VIH (min)的 Vcc x 0.3~Vcc x 0.7。

从文档来看、它的测量范围似乎是从10%到90%。

测量的电压范围是多少?

此致、

大桥