主题中讨论的其他器件: SN74AUP3G17、 SN65LVDT41、 SN74HC14、 SN74HCS125、 TXU0304

大家好!

我正在参与一个项目、该项目涉及1至2米的 SPI 通信传输距离。 该应用要求每秒从3个轴传输3200个16位大小的样本、数据速率约为154kbps。

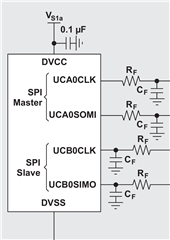

我的 SPI 配置包括采用4根导线(MISO、MOSI、SCLK 和 CS)的单个主器件和单个从器件设置。 我计划为此使用 CAT5电缆。 考虑到电缆的固有特性和所涉及的距离、我预计信号反射、EMI 和其他因素对信号完整性可能带来的挑战。

为了缓解这些挑战并实现稳健的 SPI 通信、我正在考虑使用在 SPI 连接两端具有施密特触发输入的 SN74LVC3G17缓冲器。 此缓冲器设计用于处理1.65V 至3.6V 的电源电压、并提供过压容差输入、平衡输出、并且具有超高速兼容性(tpd 5-10ns)。

我还打算考虑此配置的时钟频率。 我知道、由于信号衰减的易感性较低、较低的时钟频率可提供更佳的信号完整性。 但是、它还可能会限制数据速率。 我目前正在考虑将0.5 MHz 和2 MHz 作为可能的时钟频率。

如果有人可以分享与以下问题相关的经验、建议或顾虑、我将不胜感激:

SN74LVC3G17是否适合在此应用中用作缓冲器?

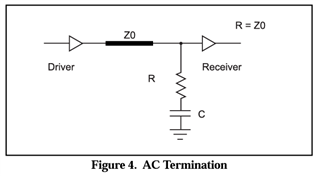

2.关于信号反射、尤其是在配置中使用此类缓冲器时、我需要考虑哪些关键注意事项?

3. 考虑到数据速率和潜在的信号完整性问题,时钟频率0.5MHz 是否太低? 或者、在给定配置下、2MHz 是否更理想?

4.是否有人对类似距离的 SPI 通信有过经验或建议、若有、有何具体建议或可能需要避免的缺陷?

提前感谢您的见解和帮助!

此致