您好!

在 VccA 通电而 VccB 未上电的情况下、A 侧的内部10Kohm 上拉电阻器处于活动状态。

OE 被拉至1.8V 侧。

我们会在启动后的稍后时间开启 VccB。 在开启 VccB 之前、我们会进行 i2c 事务、而上升时间非常慢、不对应于典型的10Kohm 上拉电阻。 除非在 B 侧未加电的情况下 A 侧 I/O 引脚上增加了电容。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

因为它是设计问题、所以它适用于所有电路板。

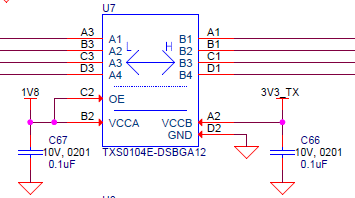

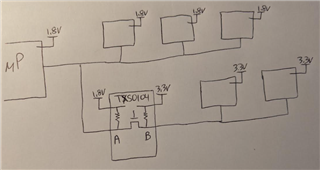

下图展示了我们的 i2c 拓扑。 在 uController 之外、我们还有1.8V i2c 总线挂起的1.8V 器件、其中 A 侧为 TXS0104E。 在 TXS0104E 之后、B 侧的3.3V i2c 总线挂起3.3V 器件。

当我们有3.3V 断电时、包括 TXS0104E 3.3V B 侧、我们的100kHz i2c 上升时间似乎具有非常弱的上拉电阻或非常大的容性负载。

那么、我的原始问题是、当 B 侧断电时、由于其上拉至1.8V、我们是否仍希望 A 侧上拉10K? A 输入是否在 B 侧断电期间与 B 侧隔离?

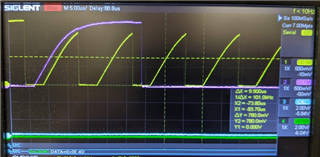

以下快照是3.3V 断电时的情况。 请注意1.8V 总线上的 i2c 上升时间。 我假设使用 TXS0104内部的10K 上拉电阻、总 C 为~30pF (每个器件引脚3pF、6pF 下的迹线为2英寸、示波器探头15pF)、我们应该可以实现更长的上升时间。 使用3*RC 可以得到3*10K*30pF = 0.900usec,即正脉宽为100kHz 的1/5。

即使上升速度很慢、但1、8V 总线仍可以正常运行、因为我们满足所有器件的 V_IH 要求。

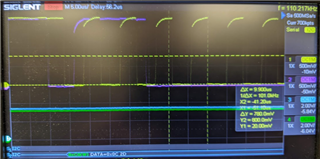

下面是当我们加电3.3V 时、TXS0104E B 侧已加电。 请注意、1.8V i2c 总线上升时间非常快。 这可能是因为一次射门踢中。 但即使没有一个射击和10K 上拉在一个侧面应该是可以的。

我又回来了。。。

我刚刚阅读了有关 TXS0104E 的主题、看起来我们将 VccB 断电、A 侧也会断电以进行隔离、这也意味着禁用10K 上拉。 您能确认吗? 另外、我在数据表中没有看到这条具体注释、除非我忽略了它。