https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1262099/txs0102-fall-time-spec

器件型号:TXS0102您好、

客户使用了 TXS0102、对下降时间测量有一些疑问、但到目前为止没有任何问题。

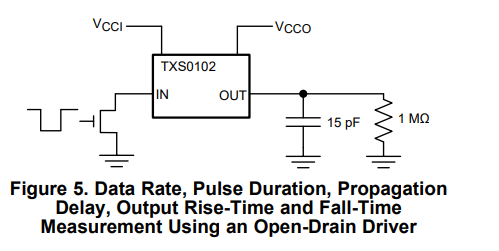

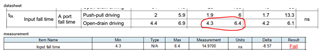

他们将其用于 i2c 1.8V <>3.3V。 DS 中有一项规格规定、端口下降时间为4.3 ~ 6.4ns。

以下是它们的测量结果:

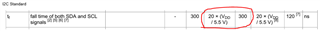

如果对结果有任何疑虑、我可以向您澄清一下吗? ×在 i2c 标准快速模式下、下降时间也可为20 μ s (VDD / 5.5V)~300ns。

谢谢。

阿兰