https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1266321/sn74lv1t125-testing-issues

器件型号:SN74LV1T125尊敬的:

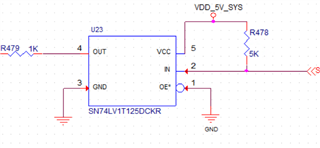

客户使用了 SN74LV1T125、电路图如下所示。

1-在测试过程中,IN 引脚未连接到任何信号。 它通过5K 电阻上拉至5V、但是测得的引脚电压低至0.5V。 我可以问一下、为什么 IN 引脚未上拉至高电平?

此芯片的输入阻抗是多少?

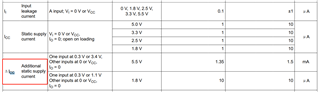

如下图所示、该参数是什么意思、如何理解它?