主题中讨论的其他器件:CD4093B

您好!

背景:

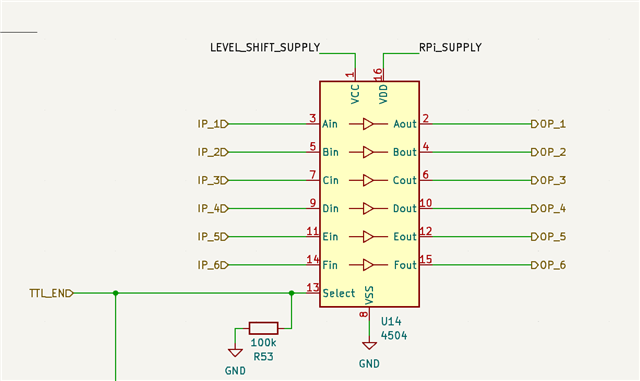

我正在使用 CD4504将 输入电平从15V、5V 或3V3等可选电源的电压电平转换为3V3 (输入始终由 与可选电源相同的电压驱动)。 我需要为我的应用同时满足 TTL 和 CMOS 输入阈值(很显然、15V TTL 不是有效条件)。 输入电路如下所示。 信号 TTL_EN 与可选电源由同一电源驱动。

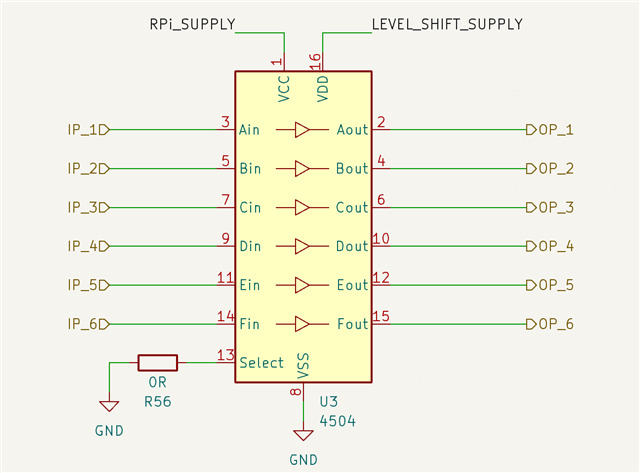

我还使用 CD4504将输出从3V3进行电平转换至可选的电源电平、同样是15V、5V 或3V3。 输出电路如下所示。

速度和功率对我的应用并不重要、但 L->H 和 H->L 开关 电压对于噪声抗扰度至关重要。 3V3信号是与我的 Raspberry PI 连接的信号。

每个 IC 在每个电源之间都有局部100nF 去耦、并且在电路板周围有良好的大容量去耦(例如10uF)。

问题:

当我改变输入电压来测试 V_IL 和 V_IH 电平时、我注意到没有迟滞。 输出开关电压大约为1.18V、并且没有迟滞(我运行的是 CMOS 到 CMOS)、并且所有输入电源电压的开关电压几乎相同(即 Vcc=15V、5V 或3v3)。 对于所有输入、Vdd 为3V3。 当我切换到输入的 TTL 模式时、L->H 转换和 H->L 转换的阈值电压都下降到了大约280mV、从抗噪的角度来看实际上是无用的。

输出的电平转换显示了相同的问题、除了开关变化的电压外、在 Vdd=3v3时大约为1.08V、在 Vdd=5V 时大约为1.62V、在 Vdd=15V 时大约为1.47V。 这次、所有输出的 Vcc=3v3。

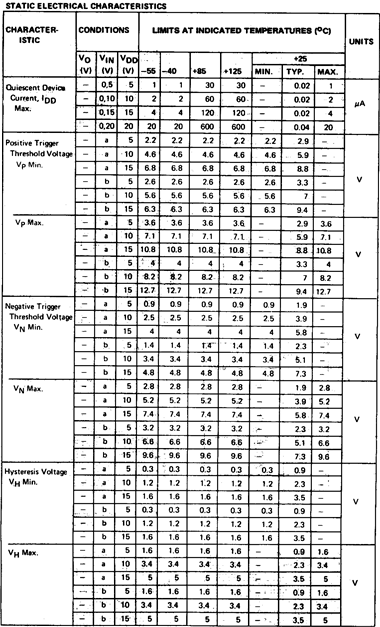

针对 V_IL (最大值)和 V_IH (最小值)、这些结果与数据表中的结果不同。

尝试解决:

CD4504产品说明书注明了建议的最低工作电压为5V、但是图形表示在3V3下工作、其他线程(例如 https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1116554/cd4504b-ep-can-cd4504b-ep-convert-15vin-to-5vout?tisearch=e2e-sitesearch&keymatch=CD4504B#) 也支持我正在做的工作原理。 目前、我怀疑设计还可以。 不过、我已经调整了一个输入芯片的电源、从5V 变为5V、以防3V3运行是个问题、但问题仍然存在。

我已检查安装的零部件是否正确、IC 上的代码是否与我预期看到的相符。 这些器件是从 Mouser 购买的、因此我预计不会出现任何虚假 IC 问题。

我想知道 IC 会损坏、可能是因为输入端未连接(不应该有、但您永远不知道在测试时是否有器件与测试连接意外断开)、因此我测试了之前未使用的通道、也出现了同样的问题。 我还测试了另一个以前没有通电的电路板。 这也显示了相同的问题、我可以确认该电路板得到了很好的处理。 处理所有器件时都采取了全面的 ESD 预防措施、因此我认为这也不是可能的原因。

致电寻求帮助!!

我看到 CD4504的已知赝像的现象是否就是这样?

我的实现、配置或操作是否有什么问题?

您是否有更适合我的应用的器件? 理想情况下、它应该具有引脚兼容性、因为我们已经构建了 PCB、但这还不是世界末日...

提前感谢!!