请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LV595A 背景如下:

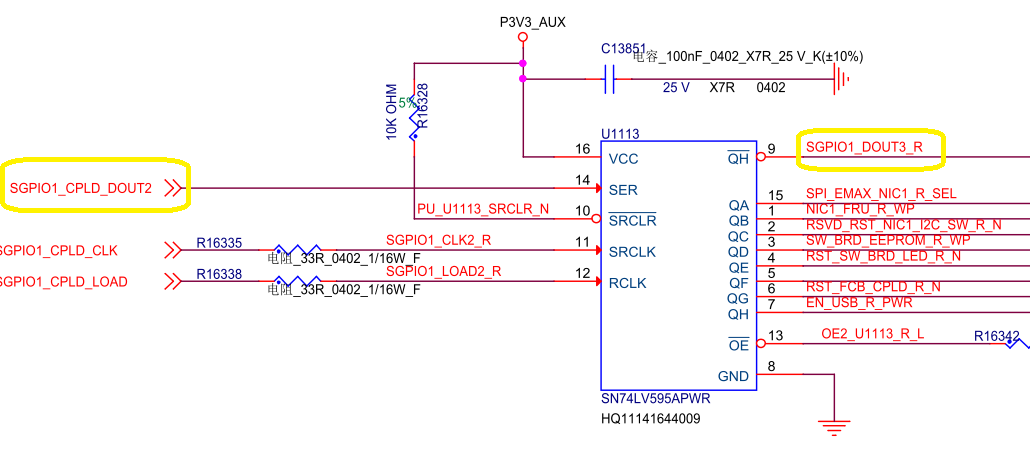

以三个为一组的方式使用 SN74LV595APWR 芯片并将其级联使用、如下所示。

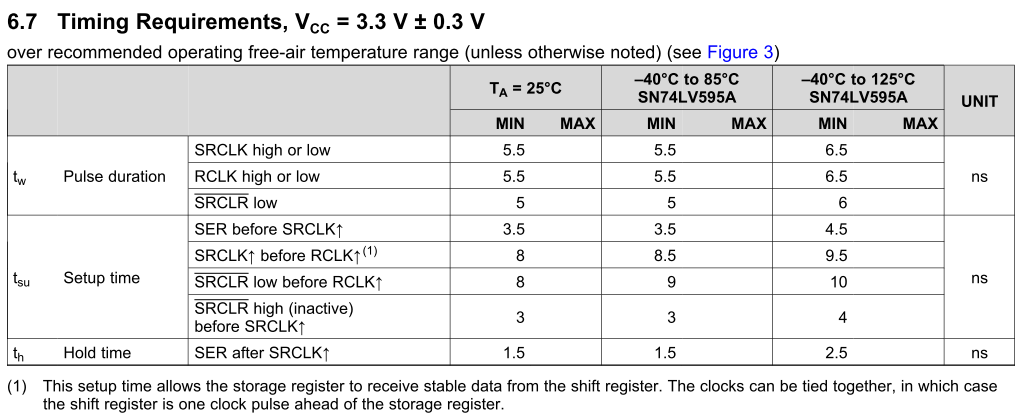

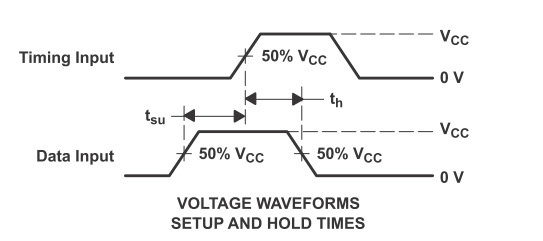

根据芯片手册的时序要求、SER 在上升沿进行采样、但从第二个芯片开始、前一个 SN74LV595APWR 的 QH'是下一个芯片的 SER。 该时间是不同的。

测得的波形与芯片手册里的时序图一致。 我想问一下、 这种情况下是否存在风险?

如果是正常的、从第二个芯片开始、 是否可以根据时钟的下降沿调整 SER 建立和保持时间? 同时按下上升沿卡值失败。 连接的是测得的波形。

从 CPLD 到前595的相关波形:

从 第一个595 到第二个595的相关波形:

C

C