主题中讨论的其他器件: AFE8190

大家好、Logic 团队、

我是在韩国的三星 NW FAE 的泰民。

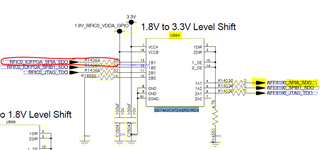

我的客户将 SN74AVC4T245设计为 USB (3.3V)和 AFE (1.8V)之间的电平转换器。

我删除了 SPIA 路径上的上拉路径、并删除了一些0欧姆用于调试、并获得了正常的 SPI 运行。

然而,只有一个电路板工作正常,其他电路板(3-4ea 电路板)运行异常。 SDO 通常没有信号、而其他 clk、en、SDIO 有时正常、有时不正常。

因此、您能否 查看随附的客户原理图和建议?

谢谢。

Taemin.