大家好!

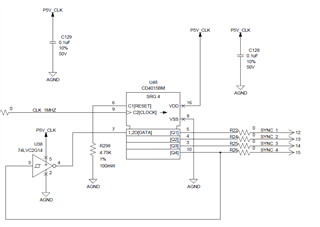

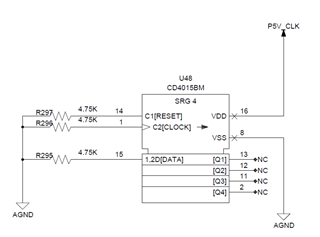

我在 设计中使用的是 CD4015B 移位寄存器、如附件的图像所示。 引脚9连接到1MHz 时钟。 对于数据输入、我们将提供 Q4的反相信号。

我们期望在每个输出 Q1、Q2、Q3和 Q4中产生250kHz 脉冲。 但我们不会看到预期的输出信号。

所有输出均为1V 直流。

我还在数据输入引脚上连接了4.7K 上拉电阻并进行了尝试(认为在初始点、输入将悬空、因此我没有获得输出)。 但输出仍然相同。

如果设计中有任何问题、任何人可以查看我的设计并为我提供帮助、或者为我提供一切建议以纠正此问题。