尊敬的专家:

了解有关 LSF 系列的内部 MOSFET 架构。 从培训视频中说这是一个四引脚 MOS、从图中可以看出、基极侧连接到 GND、栅极连接到 Vbias。

1.您能提供内部 MOSFET 的连接、施工和工作状态的详细信息吗? 视频不是很清楚。

2.根据数据表和培训视频、没有下游(B 驱动器 A)的转换波形。 您能否同时提供向上/向下波形? 由于 LSF 系列是双向 LS、因此如果将导通 FET 作为3引脚 NMOSFET 连接、则上行和下行的转换应该不同。

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的专家:

了解有关 LSF 系列的内部 MOSFET 架构。 从培训视频中说这是一个四引脚 MOS、从图中可以看出、基极侧连接到 GND、栅极连接到 Vbias。

1.您能提供内部 MOSFET 的连接、施工和工作状态的详细信息吗? 视频不是很清楚。

2.根据数据表和培训视频、没有下游(B 驱动器 A)的转换波形。 您能否同时提供向上/向下波形? 由于 LSF 系列是双向 LS、因此如果将导通 FET 作为3引脚 NMOSFET 连接、则上行和下行的转换应该不同。

谢谢

请参阅 LSF 应用报告。

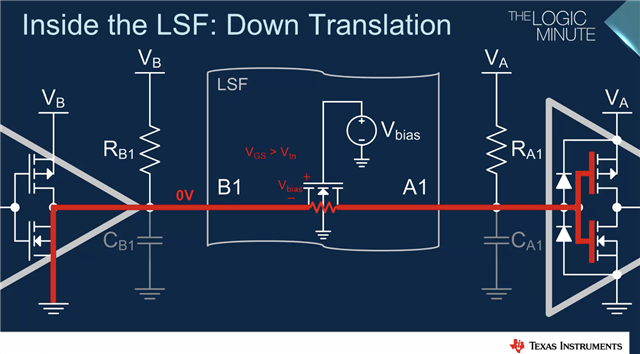

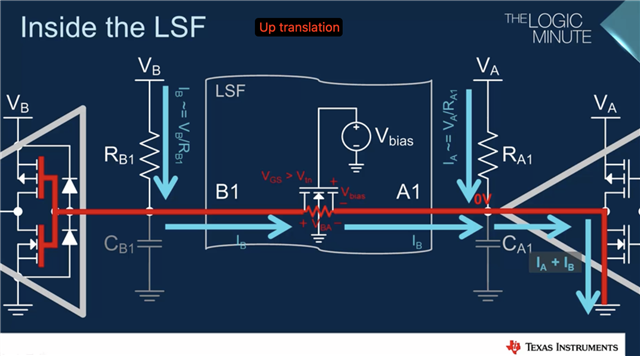

1.它们是普通的 N 沟道 MOSFET (体连接到 GND)。 你想知道什么?

2. MOSFET 是对称的;无论您将源极或漏极称为哪一侧都没有关系。 所有电压被钳位在 Vref_A 上;任何更高的输出电压必须由上拉电阻器生成。 您可以在任何 I/O 引脚上放置上拉电阻器、并且任何引脚上的上拉电压都可以不同(但不得小于 Vref_A)。

从较高的电压转换为较低的电压时、输出电压遵循输入电压、但被钳位在 Vref_A。 如果输出引脚具有上拉电阻器、则输出电压不会低于该电压。

MOSFET 是对称的;无论您称源代码还是漏代码,都无关紧要。 所有电压均钳制在 Vref_A;

使 N-MOSFET 通过 两个 n+节点之间的通道导通。 浇口和 P 衬底上的电场对于产生和维持通道非常重要。 N-MOSFET 的导通条件为 Vgs>Vth、原因是3端 MOSFET 将体连接到两个 n+节点之一、连接的节点称为 Source。 我的理解是、如果人体连接到 GND、比栅极上的 Vth 大的小电压将打开 FET。 在视频 Vgs 中、两个节点交替。 无论源/漏极在何处、它都会影响性能下降或上升转换 H2L 或 L2H。

尊敬的 Allen:

这里 Clemens"是正确的- NFET 的主体与 GND 相连、源极或漏极均无连接、其中源极/漏极可互换(将线路驱动为低电平的哪一侧可视为源极)。 此处的 Vbias 电路继续参考连接 VREFA 和 VREFB 的 NFET、从而将连接到 VREFA + VTH 的栅极电压调节到所有 I/O 通道 FET。

此致、

插孔