您好!

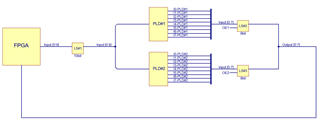

我们的设计使用了 TXS0108EQPWRQ1电平转换器、如下图:

输入[0:9]来自3.3V 电平 FPGA、并进入5V 电平 可编程逻辑器件(PLD)。 (LS#1)

每个 PLL 根据其内部逻辑创建相同的8位输出(5V 电平)。这意味着、所用的功能和 Input[0:9]是相同的。

LS#2和 LS#3上的输入[0:7]分别来自可编程逻辑器件。

每个 LS 上的输出[0:7]直接进入 FPGA 作为输入。 这很常见。

我们正在使用输出启用(OE)来激活 LS#2和 LS#3的每个输出。

我们还有一些问题:

Question:

- LS#1通常稳定且工作正常。 但是、LS#2和 LS#3无法稳定工作、它们的某些位消失了。 当我们用示波器探头触摸不工作的 IC 引脚时、该引脚会再次工作。 它真的很有趣。 您对此有什么想法吗?

- 在加电阶段、编程前;OE1和 OE2为高电平、输出端[0:7]进入 FPGA 的电平为高电平(3V3)、而输入端[0:9]进入每个 PLL 的电平再次为高电平(5V)。 PLL 根据输入[0:9]创建8位[00111110]。 因此、Ls#2和 Ls#3的信道之间存在冲突。 它是否会对电平转换器造成片刻损坏、以及它是否会导致问题1?

- 编程后、对于每个 LS、OE 为低电平。 例如、当我们决定使用 PLD#2时、只有 OE2变为高电平。 它是否正常使用;我们可以像这样使用吗?

- 在激活的 LS#2中,一些位 从 PLD#1进入输入[0:7]变为高电平。 在已激活的 LS#2中,我们看到高电平位5V 电平。 然而、在未激活 LS#3时、我们看到4V 电平来自 PLD#2。 我们预计会看到5V 电平、因为 PLDs 驱动5V 输出 Ls 将其降低至4V。 怎么可能呢?

如果您能帮助我们解决这个问题、我们将很高兴。

提前感谢。

此致、