主题中讨论的其他器件: SN74LVC1G17、SN74LVC2G17

大家好!

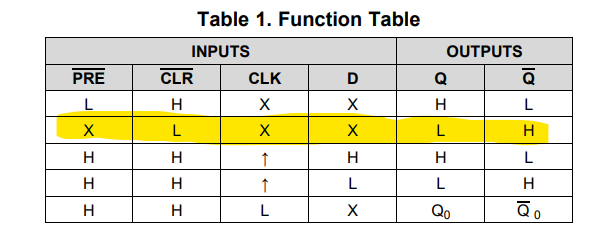

我们在应用中使用 SN74AUP1G74作为锁存器、对于此类应用、我们希望确保 IC 在上电后 Q#为高电平。 出现故障时、我们使用时钟上升沿将 Q#拉至低电平、从而关闭系统。

我们已经在 CLR#引脚(2.2K、1uF)上实施了一个 RC 延迟电路、以确保输出 Q#处于逻辑高电平已知初始状态。

因此、只有在初始上电期间、CLR#引脚才具有大于200nsec/V 的输入转换上升速率、之后它才保持高电平。 根据应用手册(https://www.ti.com/lit/ab/scea046a/scea046a.pdf?ts = 1710996273842&ref_url=https%253A%252F%252Fwww.ti.com%252Fproduct%252FSN74AUP1G79)中的图2、在这段时间内似乎有额外的电流消耗。 但是、由于此情况仅发生一次、因此我们不会看到任何热问题。 我们确保 D 和 CLK 引脚上没有任何缓慢上升输入。 请告知我们、这是否可行、或者您发现有任何问题吗?

谢谢

C. 普拉德普