Other Parts Discussed in Thread: SN74HC595

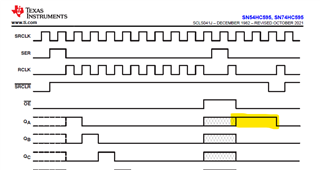

我正在使用 SN74HC595移位寄存器进行挣扎。 当 OE (输出使能)被拉至低电平时、无论命令执行何种操作、输出 Qa 都会立即开启。 我是否正确地解释了这一点:根据规格表第7页的时序图、当 OE 接地时、无论是否有其他东西、Qa 都会瞬间变为高电平?

这表明所有其他输出将保持低电平。

谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

感谢您的澄清。 很有道理。

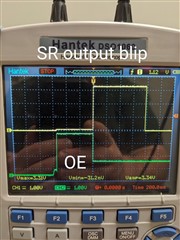

奇怪的是、我们让 Qa 自身变得越来越高、这与通过 Espressis ESP-32-Wrover 微处理器将/OE 引脚设置为低电平(我想它是低电平有效)相对应。 我已验证输出使能已接地牢固。 这股泡在约800毫秒左右,这似乎很长的计划的事情。

绿线=移位寄存器上的 OE 引脚。 最初的小曲线是电源开启、然后通过10k 上拉电阻器将其上拉至3.3V。 然后微处理器将 OE 拉为低电平。

黄线是 Qa 的输出。 我们已将所有寄存器位多次设置为0、几乎每次都没有失败。 有时所有输出都同时触发、但大多数时候只是 Qa。

此处的另一个较旧线程建议非方波时钟脉冲会导致错误行为。 这是我的时钟脉冲:

诚然、我手头没有最好的示波器、我可能需要更严格地查看这一点、并确切地了解它在做什么。