Other Parts Discussed in Thread: TXU0304, TXB0108

主题中讨论的其他器件:TXU0304、

专家、您好!

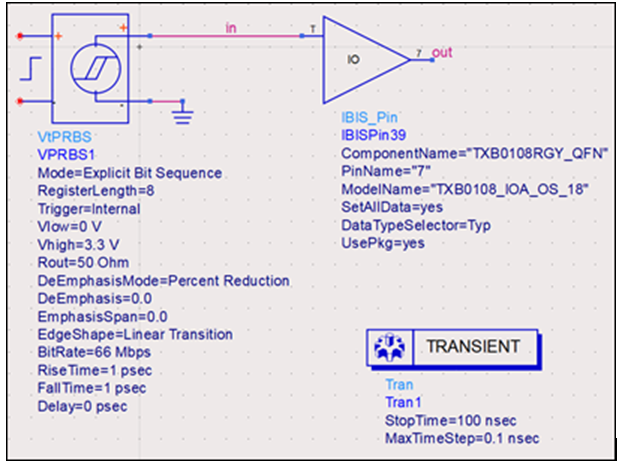

客户要求是3.3V 至1.8V、B1为3.3V、A1为1.8V。 当使用 ADS 仿真时、只能选择不同于其应用的单个引脚。 请问我们是否可以在此处使用所有8通道仿真? 非常感谢!

此致、

安连

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Clemens:

感谢您的指导。

我们目前正在单独对 A 侧和 B 侧进行模拟。 但是、我有一个有关此设置的后续问题、尤其是与在 ADS 中模拟往返延迟有关。

在上下文中、下面是我们要分析的 SPI 拓扑:

CPU--TXB0104--Com-HPC conn--Com-HPC conn--TXB0108--conn--TXB0108--MUX --MUX --MUX ---Flash

您能否提供有关如何在此配置的 ADS 中模拟总通道延迟时间和往返时间以确保准确结果的任何建议或最佳实践?

提前感谢您的帮助。

此致、

凯文