工具与软件:

大家好!

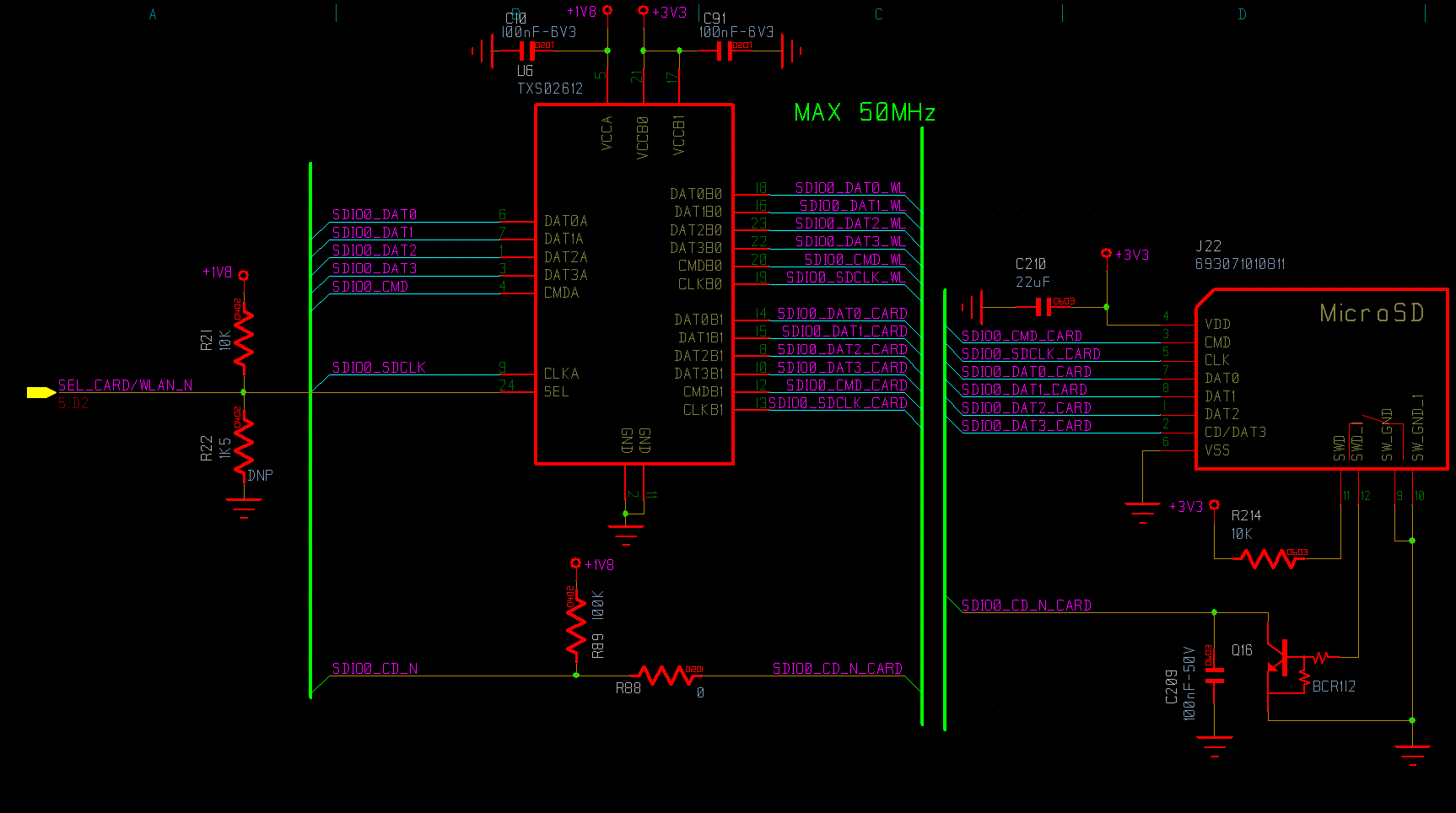

我设计了一个系统、在该系统中、uSD 卡的 SDIO 信号需要在 DS 模式(25MHz)或 HS 模式(50MHz)下从1V8转换为3V3。

通过反冲、我们发现了一个关于波形的问题。

这是我原理图的一部分:

这是25MHz 频率下的波形(红色为 SDIO0_SDCLK、黄色为 SDIO0_SDCLK_CARD):

可以看到、在3.3V (黄色)时、输出信号上存在1.5V 至2V 之间的某种过冲。

50MHz 上的内容相同:

频率为195KHz 时:

SDIO 总线信号布线的阻抗为50 Ω、长度相同。

您是否有任何建议来解释此行为?

(Teledyne ZS1500和 HFP1500有源探头用于这些测量。)

提前感谢您的支持。

此致。

Stefano Asiri。