主题中讨论的其他器件: TPS3839、 TLV840、 SN74LVC1G17

工具与软件:

大家好、团队成员:

我是 FAE Jayden、我的客户使用的是 SN74LVC1G125、他们对该器件有一个问题。

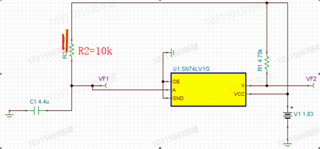

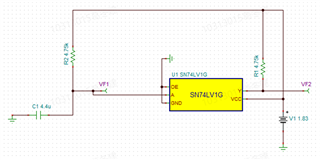

原理图如下:

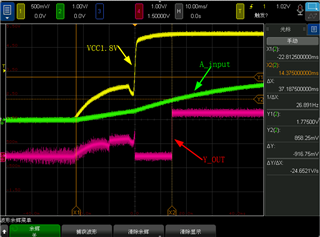

应用条件如下:PINA 使用 RC 延迟电路、 PinY 输出通过4.75k Ω 上拉至 VCC。ZTE 发现、当 PINA 输入 尚未达到 Vih=0.65* VCC 时、Y 引脚输出高电平、导致后续器件过早复位。 波形如下图:

CH1输出 Y CH2-Pina CH3-IGNORE CH4-1.8V VCC

您能帮助找出根本原因吗? 非常感谢!

祝你一切顺利

Jayden