请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G14 工具与软件:

您好!

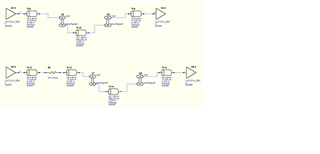

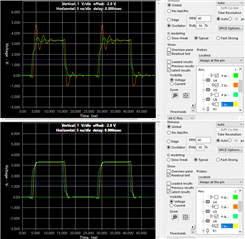

我将在进行一些信号完整性分析。 当我将74LVC 系列的输出连接到同一系列的某个器件(或任何具有高输入阻抗的其他器件)的输入时、我会在接收器处看到很大的振铃。 过去一般的做法是直接连接它们、我也从未在实践中观察到这一振铃王(通过示波器进行监控)。 我想知道这是 IBIS 文件的问题、工具问题还是仿真设置有问题。 我必须 使用49欧姆的源端接才能使信号降低(见下文)。 我感谢在这方面提供任何帮助。 如果我要使用源端接、则必须在设计中添加86个电阻器(是的、我有86个 输出直接驱动其他电路)。 下面是原理图(无端接和有端接)和波形(无端接和有端接)。

谢谢!

Tharaka。