主题中讨论的其他器件:SN74LVC1G123、

工具与软件:

尊敬的专家:

我想知道如何处理未使用的引脚。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

尊敬的专家:

我想知道如何处理未使用的引脚。

您好、Clemens:

感谢您推荐另一款器件。 但由于我的客户计划使用 SN74LV123A、因此 我们想知道如何使用此器件。

还有什么其他想法可以解决这个问题吗? 或者、我应该向客户询问一些信息吗?

顺便说一下、竞争器件(HD74LV123A)有以下 描述:

'未使用电路的输入引脚应该在用于固定输出的条件下使用、以避免出现噪声故障。 此外、建议 Rext / Cext 端子是断开的、外部器件不连接。"

https://www.renesas.com/jp/ja/document/dst/hd74lv123a-rej03d0314-0600z?language=en&r=527206

尊敬的 Malcolm:

我的客户希望仔细检查内部电路。

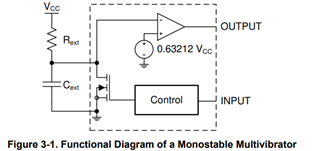

在此应用手册中、似乎只有低侧 FET 用于 Rext 和 Cext。

https://www.ti.com/jp/lit/an/slva720a/slva720a.pdf

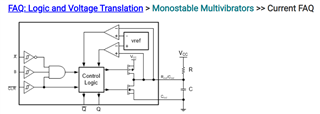

但在下面的 FQA 中、Vcc 和 Rexc/Cext 之间似乎有高侧 P-FET。 在某种情况下该 FET 导致了发热问题。

哪种配置正确?

此致

大桥