工具与软件:

大家好!

关于用于 micro-SD 卡应用的电压转换的 TXS02612有几个问题。

1) 1)下面是有关在25MHz 标准时钟速率的最坏情况下保证运行的详细问题。

2) 2)有关 VCCA 为1.8V、VCCB 为3.3V 时的通道间时钟偏斜时间为1.48ns 的简单问题;我们可以假设这意味着时钟的时间延迟比通道(数据/命令)短至少 正1.48ns 吗? 也就是说、不会为负、时钟实际上可能比通道数据的传播速度快? 这对于确保写入周期满足卡上的设置时序而不增加额外的偏差时间非常重要。

有关问题1的详细信息:

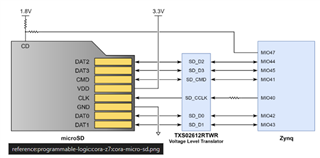

我们基于参考设计(ZC702 v1.0和 Digilent Cora Z7)设计了 AMD/Xilinx Zynq-7000转 micro-SD 卡接口。 Zynq 使用1.8V 的 MIO 接口、micro-SD 卡为3.3V。 就像其他人一样、我们使用 TI TXS02612作为它们之间的电压转换器(VT IC)。

虽然我们没有发现任何问题、但我们对设计进行了时序分析、这引起了对从卡读取数据的最坏情况下时序延迟的担忧。 这主要是由于通过 VT IC 的时钟的合并延时时间以及返回的额外数据延时。 在25MHz 时钟速率下、这些附加的 SD 卡时钟到数据输出的延迟以及 Zynq 的设置时间总共超过 SDIO 接口的20ns 时钟下降沿到上升沿。

具体细节包括:

TXS02612的 Tpd 最大值 CLKA-CLKB 为4.5ns

Tpd 最大数据 B 到 A 为6.3ns

SD 卡到数据输出的最大时钟(下降)约为12ns (根据 SD Assoc. 示例)。

这些延迟总共超过20ns、不包括 Zynq 或 PCB 布线延迟所需的4ns 设置时间。

这有道理吗? 因此、为了保证读取周期时序、我们需要将时钟减慢至18MHz。 当然、我们可以假设永远不会发生最坏的情况、并且 SD 卡的输出延迟要比12ns 快得多(这可能是一个安全的假设)。

感谢您回答这些问题。