请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74VMEH22501A 工具与软件:

大家好、

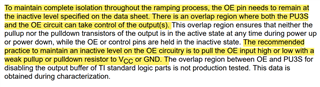

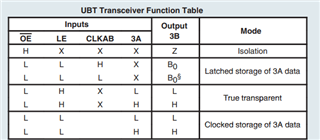

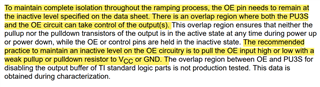

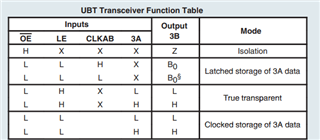

我需要对下图进行一些说明:(TI 标准逻辑器件中的*上电三态(PU3S)电路)

问:如果我根据 PU3S 更改 OE 的逻辑、那么我是否会影响我的透明模式条件?

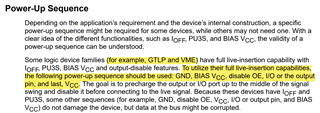

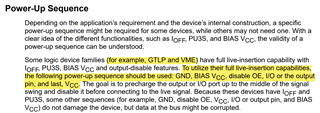

第二个查询、如何在设计中实现下面重点介绍的电源序列? 请共享相关的任何文档。

请分享您的评论。

谢谢!

Gaurav

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、

我需要对下图进行一些说明:(TI 标准逻辑器件中的*上电三态(PU3S)电路)

问:如果我根据 PU3S 更改 OE 的逻辑、那么我是否会影响我的透明模式条件?

第二个查询、如何在设计中实现下面重点介绍的电源序列? 请共享相关的任何文档。

请分享您的评论。

谢谢!

Gaurav

您好、Clemens:

感谢您的答复。

[报价用户 id="612673" url="~/support/logic-group/logic/f/logic-forum/1393988/sn74vmeh22501a-design-guidelines-for-live-insertion-using-power-up-3-state-pu3s-circuits "]第二个查询、如何在设计中实现下面重点介绍的电源序列? 请共享相关的任何文档。

请提供您对第二个查询的输入。 如何在硬件设计中实现突出的电源序列?

谢谢!

Gaurav