https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1399632/tpld1201-logic-gate-with-4-inputs

器件型号:TPLD1201工具与软件:

大家好!

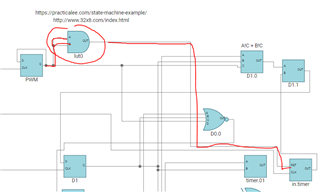

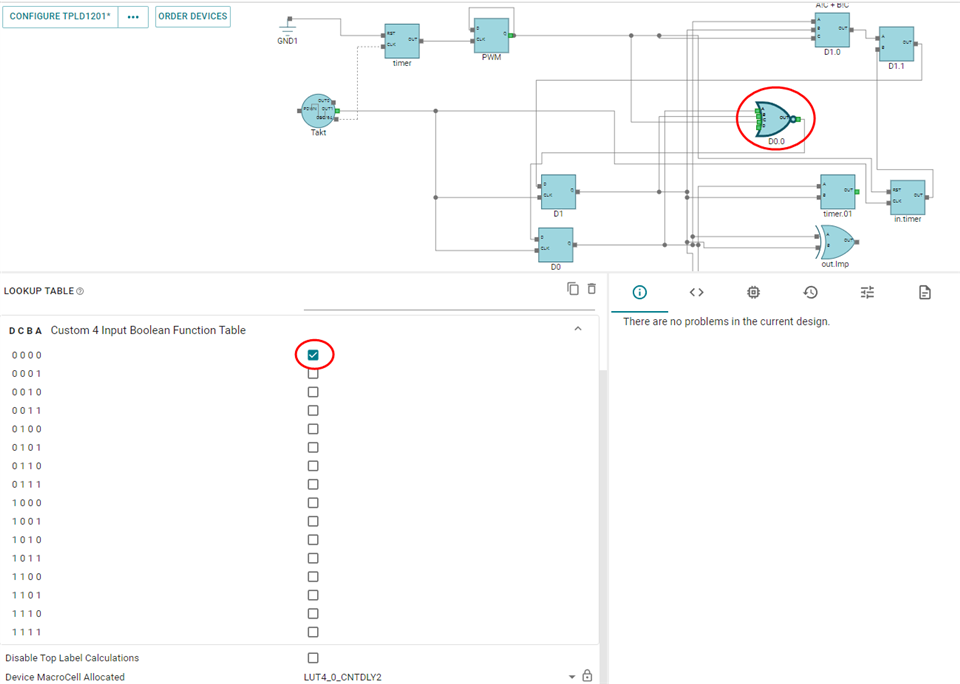

我的客户希望对我们的 TPLD1201进行编程。 他希望使用具有4个输入的逻辑门。 使用4个逻辑0 0000、他希望在输出1上实现。

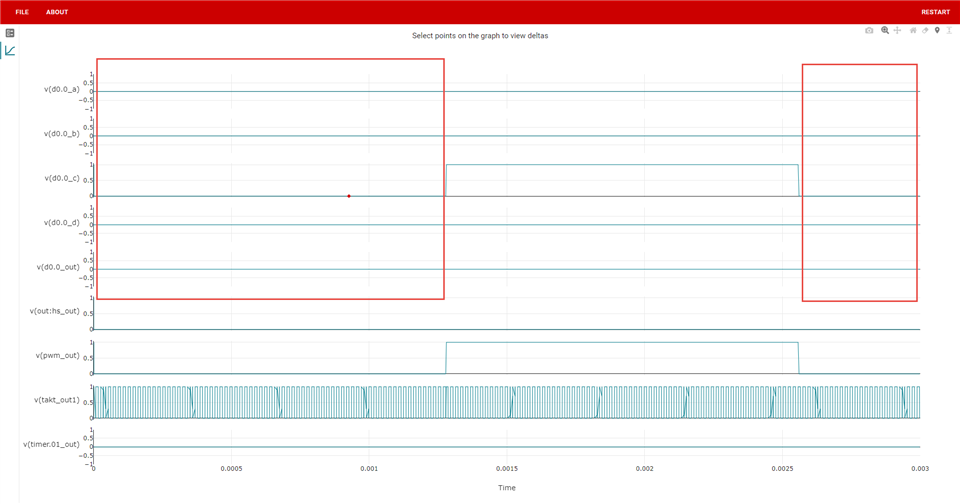

但在仿真中、客户会得到不同的结果:

这是什么原因呢? 附加了编程文件:

e2e.ti.com/.../statemachine_5F00_TI_5F00_Anfrage13082024.syscfg

此致

OLAF