Other Parts Discussed in Thread: SN74AVC4T774, SN74AXC4T774

Thread 中讨论的其他器件: SN74AXC4T774

工具与软件:

您好!

我尝试在50MHz 上运行 SPI、需要将电压从1.8V 转换为1.2V ~ 3.3V。

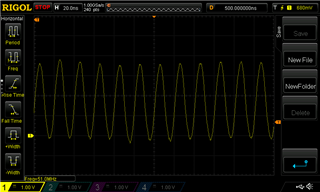

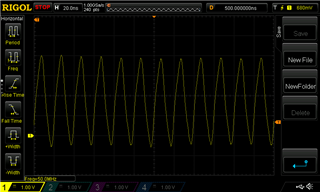

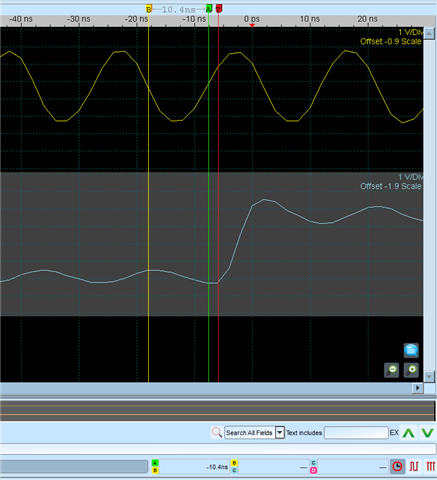

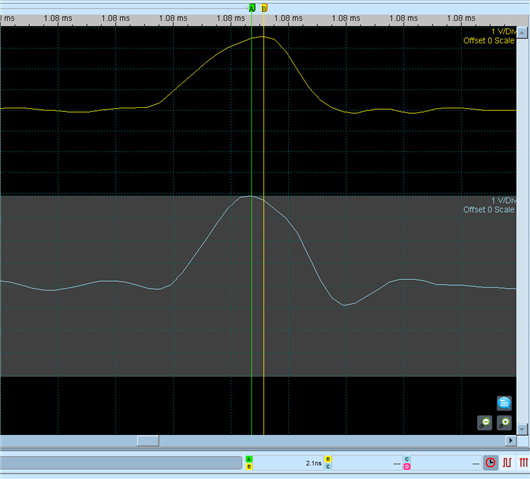

我正在使用 SN74AVC4T774、它可以在高达30MHz 的电压下完美地工作、但在进入50MHz 时却似乎出现故障。

这个 IC 不能达到这种速度? 我对传播延迟和转换上升和下降感到有点困惑。

第一个问题应该是从1.8V 转换到1.8V 时的问题、并且上升和下降时间(10ns/V)应该正确才能在高达50MHz 时正常工作、但在这些条件下、它不起作用。

我已尝试将 SPI 总线设置为3.3V、但也无法正常工作。

有什么建议?

此致、

P