请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1423891/sn74lvc1g17-sn74lvc1g32

器件型号:SN74LVC1G17工具与软件:

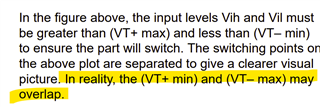

您好、此问题并非专门针对上述器件型号、而是更深入地了解施密特触发器。 我阅读了本应用手册、看到这份声明以黄色突出显示。

我是否可以知道 VT 最小值和 VT 最大值将在哪种情况下重叠?

https://www.ti.com/lit/ab/scea046a/scea046a.pdf?ts = 1728541097340