工具与软件:

我需要捕获一个上升沿并计划使用 SN74AUC74等快速逻辑器件、因为我在 TI 论坛的其他地方看到、尽管器件未指定抖动性能、但高速、低传播时间(TPP)器件可能具有低抖动。

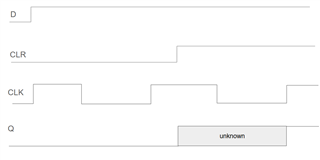

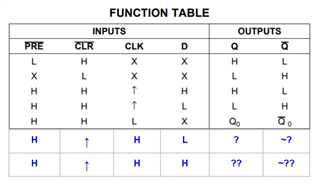

我需要选通上升沿并计划使用~CLR 引脚来提供选通功能。 当 D 连接到逻辑高电平时、应在 TPP 后的 Q 上表示~CLR 被拉至逻辑低电平后 CLK 上的下一个上升沿。 如果在 CLK 已经为逻辑高电平时将~CLR 拉至逻辑高电平、则稍后 Tprop 中将出现什么状态 Q? ~Δ V PRE 始终为逻辑高电平。

为了更方便地查看我的问题、我用蓝色字体扩展了函数表、非常感谢 TI 社区提供的帮助:

如果? = Q0 和?? = Q0、这就是我需要的结果。 如果不是、是否有任何高速/低 Tprop 器件允许门控并且只会在一个输入的上升沿(例如 CLK)改变输出?