请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1437301/txs0102-regarding-oe

器件型号:TXS0102工具与软件:

你(们)好

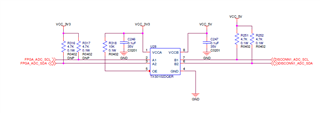

我们 在设计中使用 TXS0102DQER 来对 I2C 进行电平转换。 请告知我们是否必须下拉 OE? I2C 总线连接到 FPGA。 我们是否需要将 OE 连接到 FPGA? FPGA 上没有剩余任何引脚来连接 OE。 请告知我们这是否为强制性要求。

目前、我们已拉高 OE 以使其始终启用。 以下是我们的原理图。 另外、让我们知道我们是否可以移除 A 和 B 上 I2C 线路上的上拉电阻