https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1448851/txv0106-testing-issue

器件型号:TXV0106工具与软件:

您好!

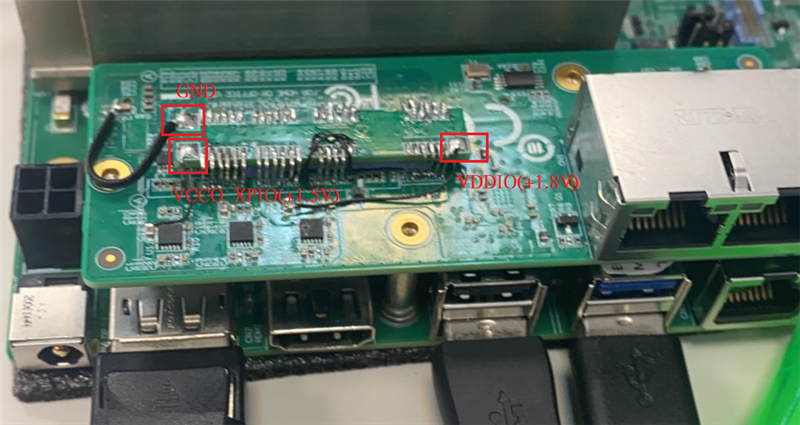

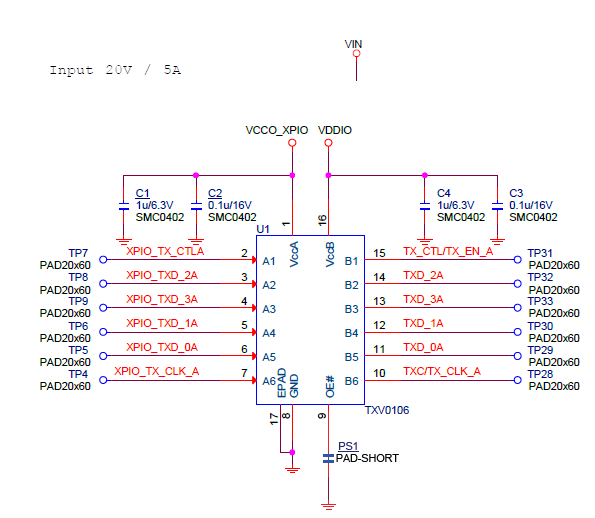

我们创建了一个小板来堆叠在原始子卡之上、以验证 TXV0106 (如下图所示)。 电路很简单、如 下图、我们有4个 TXV0106、我会通过隐私消息传递完整的原理图。

我们目前面临一个问题:

当 TXV0106 A 侧(输入)的 TXCLK 为125MHz 时、B 侧(输出)的 TXCLK (指连接的 TXCLK)。 BMP)也是125MHz。 但是、小电路板的 GND (GND. BMP)和电源(VCCO_XPI。 bmp)变得异常、如附加文件(VCC_XPIO.bmp 和 GND.bmp)所示、进而影响所有其他信号(例如 RXCLK_OUTPUT.BMP)。

当 TXCLK 降至2.5MHz 时、所有信号都恢复正常状态(请参阅 RXCLK_NOR.BMP)。

或者、如果我断开小电路板 B 侧的 TXCLK 输出(即未连接到子卡上的 PHY、但 TXCLK 仍为输出)、则不会发生问题。

1.VCC_XPIO

2. TXCLK

RXCLK_OUTPUT

4. RXCLK_NOR

5.GND

对于如何解决此问题、您有什么建议吗?

谢谢!

Jeff