https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1456762/sn74hc374-logic-forum

器件型号:SN74HC374工具与软件:

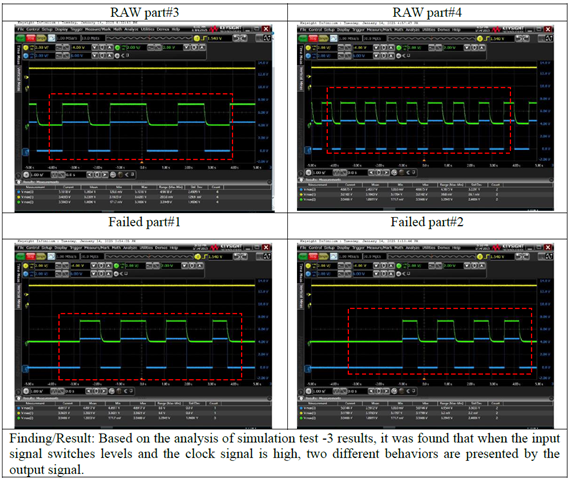

我们找到了 TI 器件 CFN320107-R (MPN: SN74HC374DWR)、顶部通道上有两个主体标记" 48CX0CK"和" 48CX1CK" 、但我们发现此器件和所有故障器件的缺陷率约为30%时标记为 Mark" 48CX1CK"、"1"和"0"有何区别?

但是我收到了以下 TI 中国工程师的反馈:

Martin